Slipstream Processors

Overview

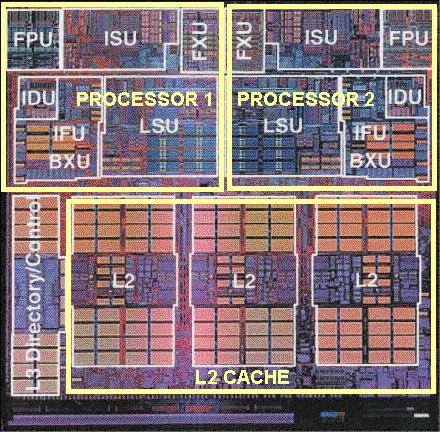

The chip multiprocessor (CMP) is an attractive substrate for future high-performance microprocessors. With multiple processors on the same chip, a CMP provides high throughput for multiprogrammed and parallel workloads. Also, each constituent processor delivers high performance for individual programs with a balanced design that achieves moderate instruction-level parallelism and a high clock rate. IBM recently integrated two processors on the same chip (below) to exploit these advantages. However, a major limitation is that a single program can use only a single constituent processor, even if the second processor is idle.

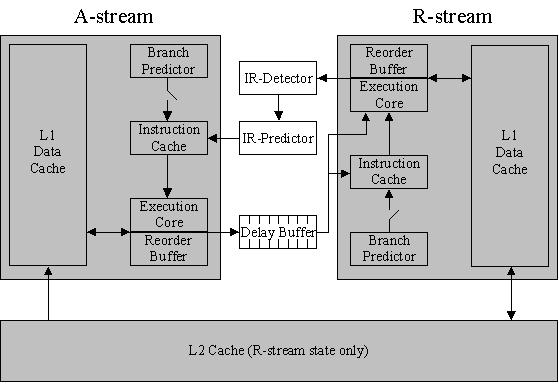

Slipstream execution provides a simple means to use a second processor in a CMP to accelerate a single program. Slipstream execution involves running two redundant copies of the program. Predicted-ineffectual computation is speculatively removed from one of the programs, speeding it up. The second program verifies the forward progress of the first and is also sped up in the process. We have demonstrated that slipstream execution on two processors of a CMP outperforms conventional execution on only one of the processors. Moreover, the redundant program arrangement also provides fault tolerance transparently and with no additional support. Slipstream execution can be implemented on a CMP substrate (below), significantly extending its capabilities.

Publications

Conference and Journal Papers

V. K. Reddy, S. Parthasarathy, and E. Rotenberg. Understanding Prediction-Based Partial Redundant Threading for Low-Overhead, High-Coverage Fault Tolerance. Proceedings of the 12th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS-XII), pp. 83-94, October 2006. [pdf]

J. J. Koppanalil and E. Rotenberg. A Simple Mechanism for Detecting Ineffectual Instructions in Slipstream Processors. IEEE Transactions on Computers, 53(4):399-413, April 2004.

Z. Purser, K. Sundaramoorthy, and E. Rotenberg. A Study of Slipstream Processors. Proceedings of the 33rd IEEE/ACM International Symposium on Microarchitecture (MICRO-33), pp. 269-280, December 2000. [pdf]

K. Sundaramoorthy, Z. Purser, and E. Rotenberg. Slipstream Processors: Improving both Performance and Fault Tolerance. Proceedings of the 9th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS-9), pp. 257-268, November 2000. [pdf]

Eric Rotenberg. AR-SMT: A Microarchitectural Approach to Fault Tolerance in Microprocessors. Proceedings of the 29th IEEE International Symposium on Fault-Tolerant Computing (FTCS-29), pp. 84-91, June 1999. [pdf]

Technical Reports

Z. Purser, K. Sundaramoorthy, and E. Rotenberg. Slipstream Memory Hierarchies. Technical Report CESR-TR-02-3, Center for Embedded Systems Research, Department of Electrical and Computer Engineering, North Carolina State University, February 2002. [pdf]

K. Sundaramoorthy, Z. Purser, and E. Rotenberg. Multipath Execution on Chip Multiprocessors Enabled by Redundant Threads. Technical Report CESR-TR-01-2, Center for Embedded Systems Research, Department of Electrical and Computer Engineering, North Carolina State University, October 2001. [pdf]

Eric Rotenberg. Exploiting Large Ineffectual Instruction Sequences. Technical Report, North Carolina State University, November 1999. [pdf]

Student Theses

S. Parthasarathy. Improving Transient Fault Tolerance of Slipstream Processors. M.S. Thesis, Department of Electrical and Computer Engineering, North Carolina State University, December 2005. [NCSU library: on-line thesis]

Z. R. Purser. Slipstream Processors. Ph.D. Thesis, Department of Electrical and Computer Engineering, North Carolina State University, July 2003. [NCSU library: on-line dissertation]

N. Gupta. Slipstream-Based Steering for Clustered Microarchitectures. M.S. Thesis, Department of Electrical and Computer Engineering, North Carolina State University, May 2003. [pdf]

J. J. Koppanalil. A Simple Mechanism for Detecting Ineffectual Instructions in Slipstream Processors. M.S. Thesis, Department of Electrical and Computer Engineering, North Carolina State University, May 2002. [pdf]

Publications from Related Projects

K. Z. Ibrahim, G. T. Byrd, and E. Rotenberg. Slipstream Execution Mode for CMP-Based Multiprocessors. Proceedings of the 9th IEEE International Symposium on High-Performance Computer Architecture (HPCA-9), pp. 179-190, February 2003. [pdf]

Talks

Conference Talks

A Study of Slipstream Processors. Presented at MICRO-33 by Z. Purser. [pdf]

Slipstream Processors: Improving both Performance and Fault Tolerance. Presented at ASPLOS-9 by E. Rotenberg. [pdf]

AR-SMT: A Microarchitectural Approach to Fault Tolerance in Microprocessors. Presented at FTCS-29 by E. Rotenberg. [pdf]

Industry Talks

Cooperative Redundant Threads (CRT). Presented at IBM-T.J.Watson (July 28, 2000), Compaq-Shrewsbury (July 31, 2000), and Compaq-Marlborough (August 1, 2000). [pdf]

Exploiting Multiple On-Chip Contexts in New Ways. Presented at Intel-MRL (January 2000). [pdf]

Funding

This project is supported by NSF CAREER grant No. CCR-0092832 (CAREER: Cooperative Redundant Threads), and generous funding and equipment donations from Intel.

A related project, which explores slipstream execution mode for parallel systems, is supported by NSF grants CCR-0105628 (New Prediction Paradigms for Parallel and Distributed Systems) and CCR-0310847 (Multiprocessor Performance Optimization using Slipstream Execution Mode).

Any opinions, findings, and conclusions or recommendations expressed in this website and publications herein are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.