Research

Current Research Projects

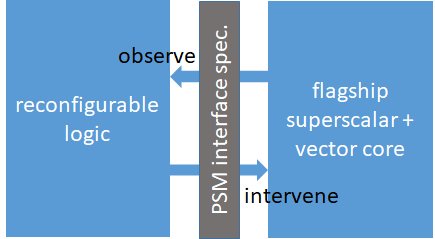

Post-Silicon Microarchitecture

Slipstream Processors 2.0

New Branch Architectures

Past Research Projects (listed most recent to least recent)

Design for Competitive Automated Layout (DCAL)

Please stay tuned – I’m currently adding a dedicated sit for this past project.

H3: A 3D Heterogeneous Multi-core Processor

We are currently researching applications and fabricating prototypes of H3, a 3D heterogeneous multi-core processor. We have measured under 100-cycle thread migration latency between two heterogeneous OOO cores in both a precursor 2D chip and the final 3D chip.

AnyCore

AnyCore is a synthesizable RTL and UPF model of an adaptive superscalar core. We are doing both research and chip fabrication with AnyCore.

FabScalar

A heterogeneous multi-core processor (or asymmetric multi-core processor) provides multiple, differently-designed superscalar core types that can streamline the execution of diverse programs and program phases. Providing multiple superscalar core types on a chip is an exciting new direction for increasing performance and reducing power, as conventional technology and microarchitecture scaling slows. This paradigm has an “Achilles’ Heel”, however: design and verification effort is multiplied by the number of different core types. The FabScalar project is the first to bring solutions to bear on this problem, and explores a number of other intriguing questions and challenges with respect to architecting heterogeneous multi-core processors.

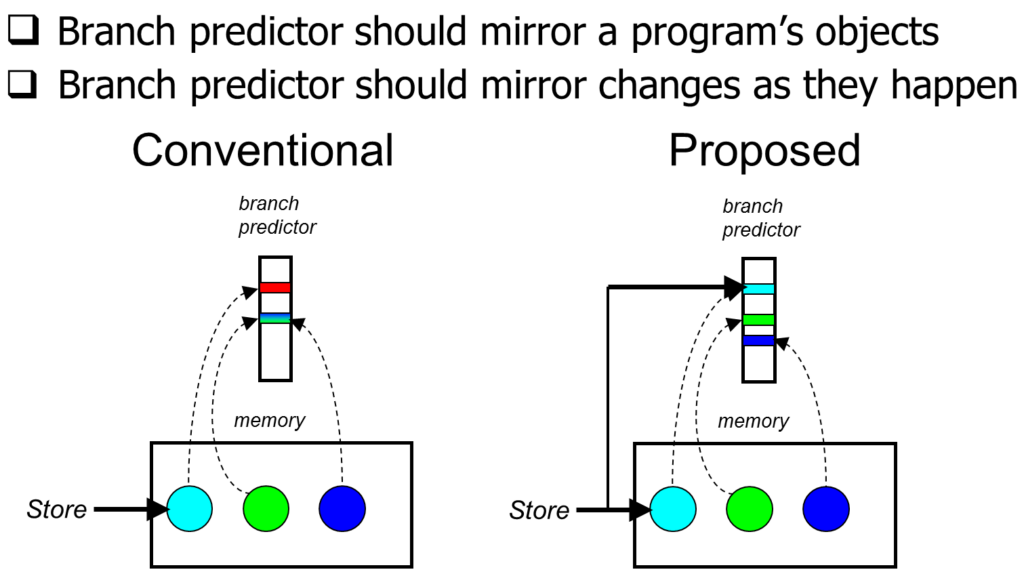

Object-Driven Execution

In this project, we explore novel microarchitectures on multi-core substrates and novel microarchitecture mechanisms for accelerating single-thread performance. The theme is to accelerate computation that iterates over a program’s objects and also react to changes in these objects before they are revisited.

Low-Power Memory

The importance of mass storage cannot be overstated. Most users really care about their files and information. Computer architectures are heavily influenced by parameters imposed by memory technologies. We are interested in all parameters of mass storage (volatility, speed, power, density, cost, reliability) and intrigued by the diversity of prevailing and nascent memory technologies. In the near term, since mass storage is increasingly important in portable devices, we are investigating ways of achieving very low-power memory, exploiting both conventional technologies (e.g., DRAM) and more exotic ones.

Architectures for Real-Time

Due to increasing functionality in cell phones, cameras, cars, and other embedded systems, high-end embedded processors are inheriting high-performance techniques from their desktop counterparts, such as pipelining, caches, dynamic branch prediction, and multithreading. Unfortunately, while these techniques perform well on average, their performance cannot be analytically bounded, a key safety requirement for embedded systems with real-time tasks. In this project, we are pioneering new directions for designing higher performance real-time embedded systems without compromising safety.

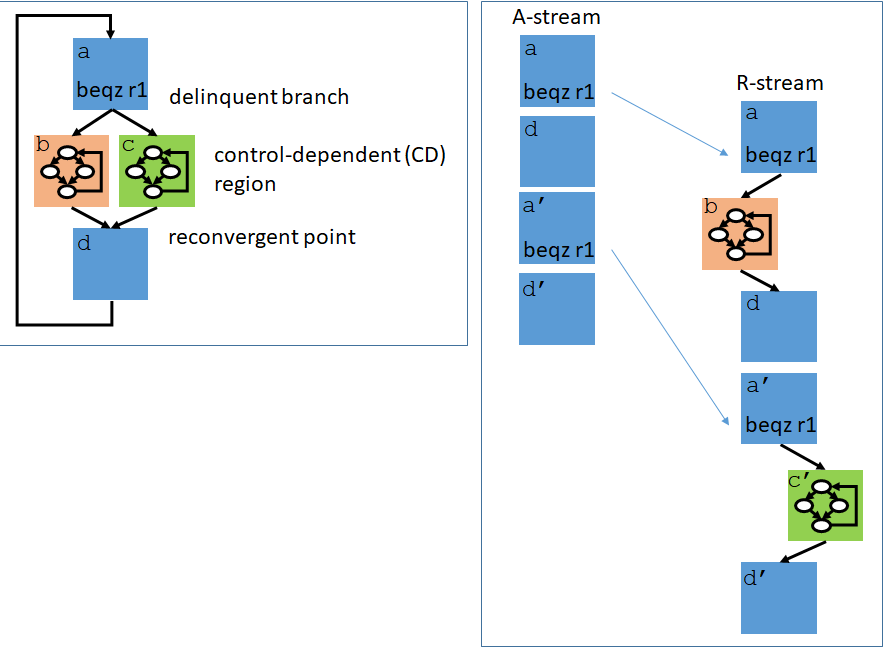

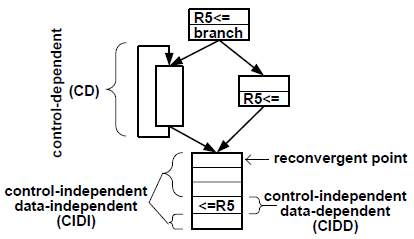

Control-Flow Processors

In the area of high-performance processors, there remain only a few dogged bottlenecks that fundamentally constrain performance, i.e., these bottlenecks render additional millions of transistors mostly ineffective. This project attacks one of the remaining grand-challenge problems in scaling microprocessor performance: ambiguous control-flow

Fault-Tolerant Architectures

There is growing concern that transient faults, caused by cosmic rays and other factors, will occur frequently in future high-performance processors, as designers push technology to its extreme limits. Existing fault-tolerant techniques are either too costly (system-level replication), too intrusive (gate-level replication), or too specific (e.g., ECC on memory). In 1999, we proposed a microarchitectural approach to fault tolerance (AR-SMT), achieving broad coverage of transient faults with low performance overhead and few changes to the underlying microarchitecture. We revisit this notion and explore other ways the microarchitecture can help reliability.

Slipstream Processors

This project investigates new ways to exploit chip multiprocessors (CMP) and simultaneous multithreading processors (SMT), and expand their capabilities. The ability to execute multiple tasks at the same time within a single microprocessor chip opens up major opportunities for increasing the performance, functionality, and reliability of computers