## Abstract

#### GUPTA, NIKHIL

# Slipstream-Based Steering for Clustered Microarchitectures

(Under the direction of Dr. Eric Rotenberg)

To harvest increasing levels of ILP while maintaining a fast clock, clustered microarchitectures have been proposed. However, the fast clock enabled by clustering comes at the cost of multiple cycles to communicate values among clusters. A chief performance limiter of a clustered microarchitecture is inter-cluster communication between instructions. Specifically, inter-cluster communication between critical-path instructions is the most harmful. The slipstream paradigm identifies critical-path instructions in the form of effectual instructions.

We propose eliminating virtually all inter-cluster communication among effectual instructions, simply by ensuring that the entire effectual component of the program executes within a cluster. This thesis proposes two execution models: the *replication model* and the *dedicated-cluster model*. In the replication model, a copy of the effectual component is executed on each of the clusters and the ineffectual instructions are shared among the clusters. In the dedicated-cluster model, the effectual component is executed on a single cluster (the *effectual cluster*), while all ineffectual instructions are steered to the remaining clusters. Outcomes of ineffectual instructions are not needed (in hindsight), hence their execution can be exposed to inter-cluster communication latency without significantly impacting overall performance.

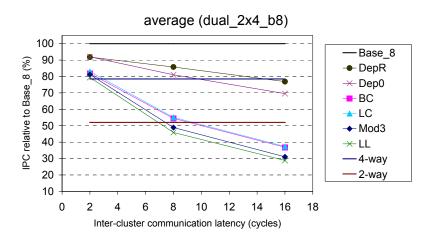

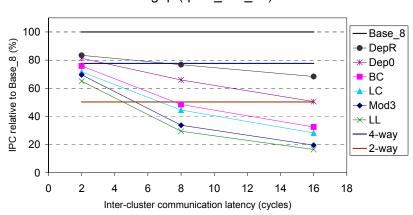

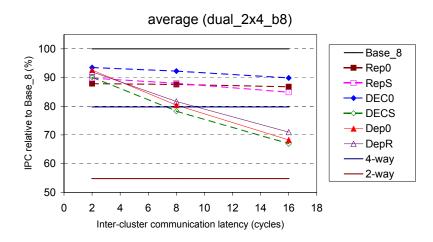

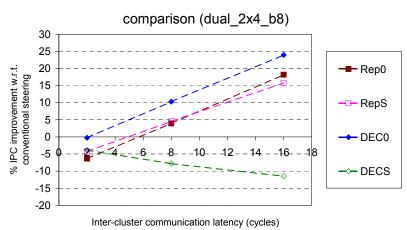

IPC of the replication model on dual clusters and quad clusters is virtually independent of inter-cluster communication latency. IPC decreases by 1.3% and 0.8%,

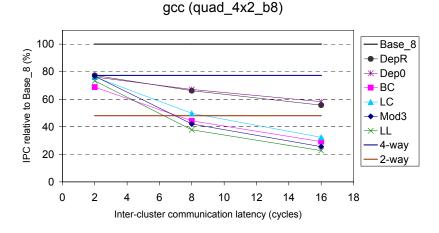

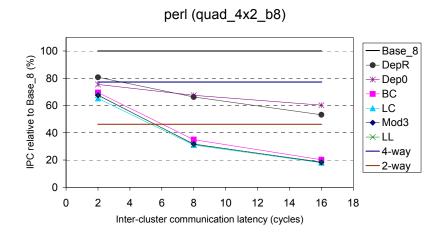

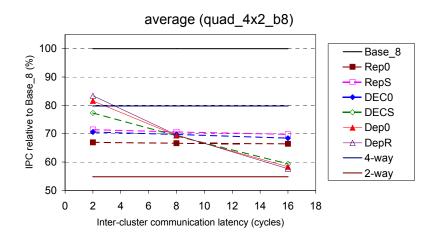

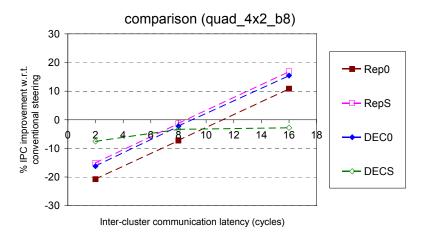

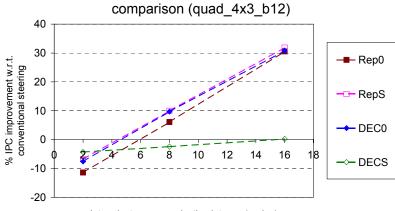

on average, for a dual-cluster and quad-cluster microarchitecture, respectively, when inter-cluster communication latency increases from 2 cycles to 16 cycles. In contrast, IPC of the best-performing dependence-based steering decreases by 35% and 55%, on average, for a dual-cluster and quad-cluster microarchitecture, respectively, over the same latency range. For dual clusters and quad clusters with low latencies (fewer than 8 cycles), slipstream-based steering underperforms conventional steering because improved latency tolerance is outweighed by higher contention for execution bandwidth within clusters. However, the balance shifts at higher latencies. For a dual-cluster microarchitecture, dedicated-cluster-based steering outperforms the best conventional steering on average by 10% and 24% at 8 and 16 cycles, respectively. For a quad-cluster microarchitecture, replication-based steering outperforms the best conventional steering on average by 10% and 32% at 8 and 16 cycles, respectively.

Slipstream-based steering desensitizes the IPC performance of a clustered microarchitecture to tens of cycles of inter-cluster communication latency. As feature sizes shrink, it will take multiple cycles to propagate signals across the processor chip. For a clustered microarchitecture, this implies that with further scaling of feature size, the inter-cluster communication latency will increase to the point where microarchitects must manage a distributed system on a chip. Thus, if individual clusters are clocked faster, at the expense of increasing inter-cluster communication latency, performance of a clustered microarchitecture using slipstream-based steering will improve considerably as compared to a clustered microarchitecture using the best conventional steering approach.

## **Slipstream-Based Steering for Clustered Microarchitectures**

by

### Nikhil Gupta

#### A thesis submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Master of Science

#### **COMPUTER ENGINEERING**

Raleigh

2003

Approved by

Dr. Eric Rotenberg, Chair of Advisory Committee

Dr. Gregory T. Byrd

Dr. Thomas M. Conte

## BIOGRAPHY

Nikhil Gupta was born on December 31, 1979, in Amritsar, India. He graduated with a Bachelor of Engineering (B.E.) degree in Instrumentation and Control Engineering from Nirma Institute of Technology (affiliated with Gujarat University), Ahmedabad, India, in June 2001.

In fall 2001, he joined the masters program in Computer Engineering at North Carolina State University, Raleigh, NC. He was part of the slipstream project and completed his masters thesis under the direction of Dr. Eric Rotenberg.

### ACKNOWLEDGEMENT

I would like to dedicate this thesis to my parents Yash and Ashoki. My father, for his boundless (well almost) knowledge, which never ceases to amaze and inspire me. My mother, under whose meticulous care, life has been such a breeze. Their love and encouragement means a lot to me. My sister Richa, who with her effervescent smile lights up our family. I would like to thank Shubha for her love and constant support.

I would really like to thank Dr. Eric Rotenberg for having provided me with this opportunity to work with him. Working for him has been a pleasant and fantastic learning experience. He is easily one of the best teachers I have ever studied under (though he has not heard me say that). His ability to breakdown the most complex of problems and explain them even to a layman always amazes me. I have learnt a lot from him about computer architecture, better writing, and a good work ethic.

I would like to thank Dr. Greg Byrd and Dr. Tom Conte for agreeing to be on my Masters thesis committee.

I would also like to thank Sandy Bronson for all that she does to make the life of all of us students easy.

I would like to thank Aravindh Anantaraman, Karthik Sunadaramoorthy, Prakash Ramrakhyani, and Zach Purser for making the working environment (first) in EGRC 438 and (then) in Partners-I, as friendly as it could possibly be. Their invaluable insights and regular help that they provided on the simulator and other practical aspects was always very helpful. I would also like to thank Huiyang Zhou, Mark Toburen, Saurabh Sharma, and Ugur Gunal for providing a ready ear for my doubts.

I would also like to thank the technical support team of the Electrical and Computer Engineering department, who were always prompt in solving my problems.

I would like to thank Aaditya Goswami, Viraj Mehta, and Vikas Garg for having put up with my cooking, erratic behavior, bad jokes and an occasional mania for cleanliness, all of these two years. A special thanks to Chintan Trivedi, Harshit Shah, Manas Somaiya, Jinal Dalal, and Vishal Khanderia for making the transition of living in a new country, a new environment so easy. I have always valued their friendship and advice and will continue to do so in the future. A special thanks to Shalin Dalal, Magathi Jayaram, Rachana Shah, and Rachana Doshi for their friendship.

## INDEX

| List of Figures                                                                                   | vii  |

|---------------------------------------------------------------------------------------------------|------|

| List of Tables                                                                                    | xii  |

| 1       Introduction         1.1       Contributions         1.2       Organization of the Thesis | 5    |

| 2 Processors with a Clustered Microarchitecture                                                   | 9    |

| 2.1 Clustered Microarchitecture.                                                                  | . 11 |

| 2.1.1 Number of write ports to a cluster register file                                            |      |

| 2.1.2 Number of read ports to a cluster register file                                             |      |

| 2.2 Bottlenecks in a Clustered Microarchitecture                                                  |      |

| 2.3 Steering Heuristics                                                                           |      |

| 3 Slipstream Components used for Steering                                                         | . 21 |

| 3.1 IR-predictor                                                                                  |      |

| 3.2 IR-detector                                                                                   | 23   |

| 3.3 Use of IR-detector/IR-predictor in Steering Mechanisms                                        | 24   |

| 4 Thesis Contribution: Slipstream-Based Steering                                                  |      |

| 4.1 Replication of Effectual Component (Rep0)                                                     |      |

| 4.1.1 Implications of redundant execution                                                         | 28   |

| 4.1.2 Regarding memory disambiguation                                                             | . 29 |

| 4.1.3 Implication of IR-mispredictions                                                            | . 30 |

| 4.1.4 Changes to the microarchitecture                                                            | . 30 |

| 4.2 Replication of Effectual Component with Store Distribution (RepS)                             | 31   |

| 4.3 Dedicated Cluster for Effectual Component (DEC0)                                              | . 34 |

| 4.4 Dedicated Cluster for Effectual Component with Store Distribution (DECS)                      | 36   |

| 5 Simulation Methodology                                                                          | . 39 |

| 5.1 Microarchitecture Configuration                                                               | . 39 |

| 5.2 Benchmarks                                                                                    | 41   |

| 6 Experimental Results                                                                            | . 42 |

| 6.1 Conventional steering                                                                         | . 43 |

| 6.1.1 Dual_2x4_b8                                                                                 | . 44 |

| 6.1.2 Quad $4x2b8$                                                                                | . 48 |

| 6.1.3 $Quad[4x3]b12$                                                                              |      |

| 6.2 Slipstream-based steering                                                                     | . 54 |

| 6.2.1 Dual_2x4_b8                                                                                 | 57   |

| 6.2.1.1 Trends among slipstream-based steering                             | 57  |

|----------------------------------------------------------------------------|-----|

| 6.2.1.2 Comparison of slipstream-based steering with conventional steering | 58  |

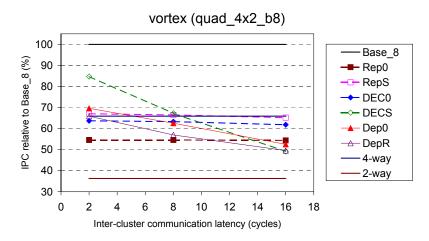

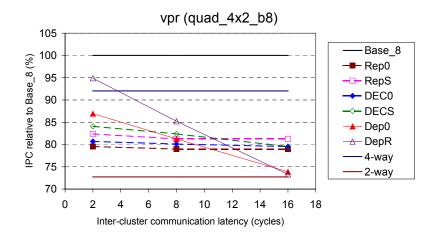

| 6.2.2 Quad_4x2_b8                                                          | 63  |

| 6.2.2.1 Trends among slipstream-based steering                             | 64  |

| 6.2.2.2 Comparison of slipstream-based steering with conventional steering | 65  |

| 6.2.3 Quad_4x3_b12                                                         | 69  |

| 6.2.3.1 Trends among slipstream-based steering                             | 70  |

| 6.2.3.2 Comparison of slipstream-based steering with conventional steering | 72  |

|                                                                            |     |

| 7 Related Work                                                             | .77 |

|                                                                            |     |

| 8 Summary and Future Work                                                  | 81  |

| 8.1 Summary                                                                | 81  |

| 8.2 Future Work                                                            | 83  |

|                                                                            |     |

| Bibliography                                                               | 87  |

|                                                                            |     |

| Appendix                                                                   | 89  |

# List of Figures

| Figure 1-1: Replication model of instruction execution in a clustered microarchitecture | 4    |

|-----------------------------------------------------------------------------------------|------|

| Figure 1-2: Dedicated-cluster model of instruction execution in a clustered             |      |

| microarchitecture.                                                                      | 5    |

| Figure 2-1: Comparison between a non-clustered microarchitecture and a quad-clustered   | ed   |

| microarchitecture.                                                                      | . 12 |

| Figure 4-1: A breakdown of the dynamic instruction stream.                              |      |

| Figure 4-2: Replication of the effectual component.                                     |      |

| Figure 4-3: A breakdown of the dynamic instruction stream.                              |      |

| Figure 4-4: Replication of effectual component with store distribution                  | . 33 |

| Figure 4-5: Dedicated cluster for effectual component.                                  | . 35 |

| Figure 4-6: Dedicated cluster for effectual component with store distribution           | . 38 |

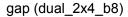

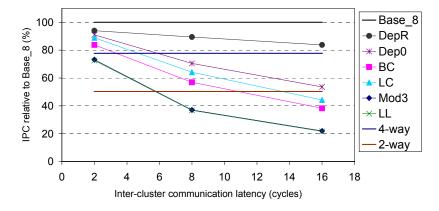

| Figure 6-1: Relative performance of conventional steering on dual_2x4_b8, with respe    | ct   |

| to Base_8, for <i>gap</i>                                                               | . 45 |

| Figure 6-2: Relative performance of conventional steering on dual_2x4_b8, with respe    | ct   |

| to Base_8, for gcc.                                                                     | . 45 |

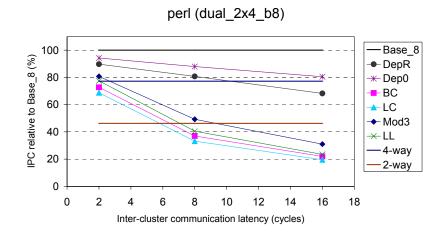

| Figure 6-3: Relative performance of conventional steering on dual_2x4_b8, with respe    | ct   |

| to Base_8, for <i>perl</i>                                                              | . 46 |

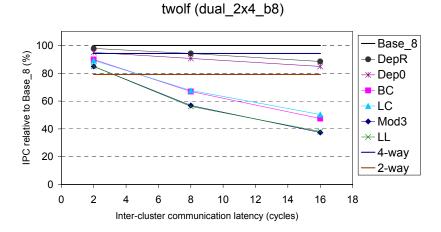

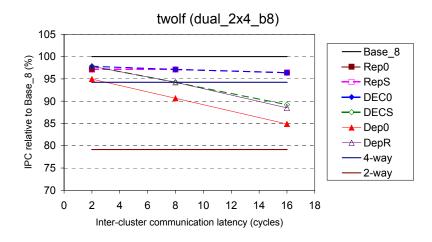

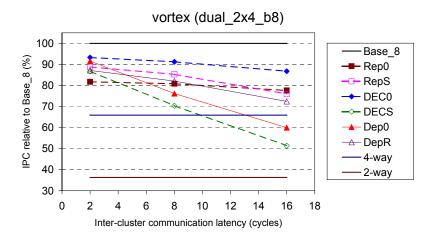

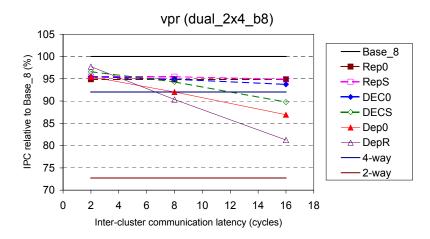

| Figure 6-4: Relative performance of conventional steering on dual_2x4_b8, with respe    | ct   |

| to Base_8, for <i>twolf</i>                                                             | . 46 |

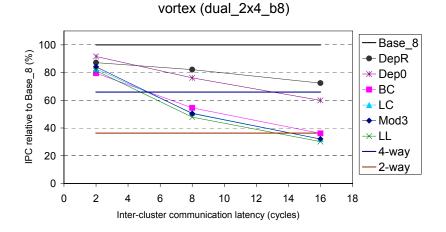

| Figure 6-5: Relative performance of conventional steering on dual_2x4_b8, with respe    | ct   |

| to Base_8, for <i>vortex</i>                                                            | . 46 |

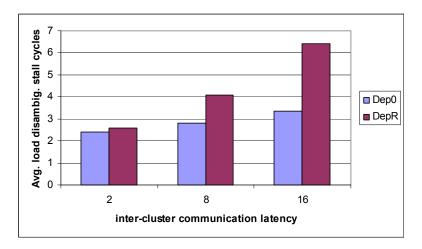

| Figure 6-6: Average load disambiguation stall cycles of Dep0 and DepR on dual_2x4_      | b8,  |

| for <i>perl</i> .                                                                       | . 47 |

| Figure 6-7: Relative performance of conventional steering on dual_2x4_b8, with respe    | ct   |

| to Base_8. Results are averaged across five benchmarks.                                 |      |

| Figure 6-8: Relative performance of conventional steering on quad_4x2_b8, with respe    | ect  |

| to Base_8, for gap                                                                      |      |

| Figure 6-9: Relative performance of conventional steering on quad_4x2_b8, with respe    | ect  |

| to Base_8, for gcc.                                                                     | . 49 |

| Figure 6-10: Relative performance of conventional steering on quad_4x2_b8, with         |      |

| respect to Base 8, for <i>perl</i> .                                                    | . 50 |

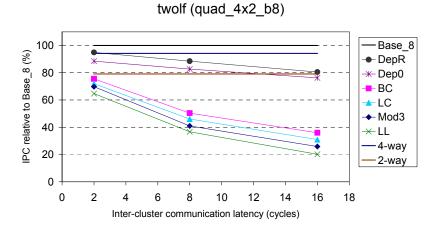

| Figure 6-11: Relative performance of conventional steering on quad 4x2 b8, with         |      |

| respect to Base_8, for <i>twolf</i>                                                     | . 50 |

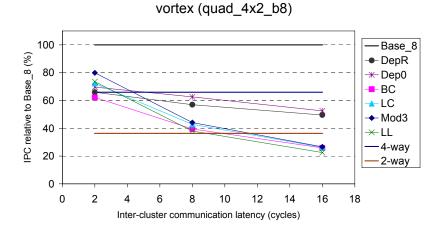

| Figure 6-12: Relative performance of conventional steering on quad_4x2_b8, with         |      |

| respect to Base 8, for <i>vortex</i> .                                                  | . 50 |

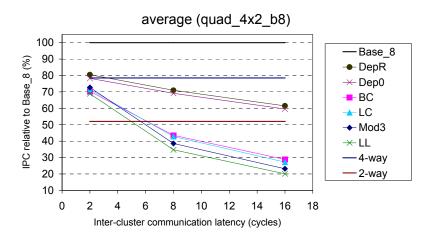

| Figure 6-13: Relative performance of conventional steering on quad 4x2 b8, with         |      |

| respect to Base_8. Results are averaged across five benchmarks                          | . 51 |

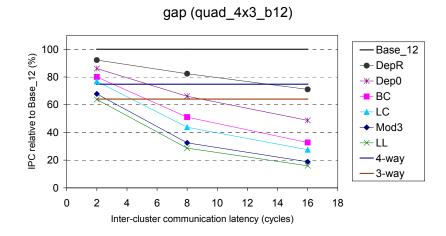

| Figure 6-14: Relative performance of conventional steering on quad_4x3_b12, with        |      |

| respect to Base 12, for <i>gap</i>                                                      | . 52 |

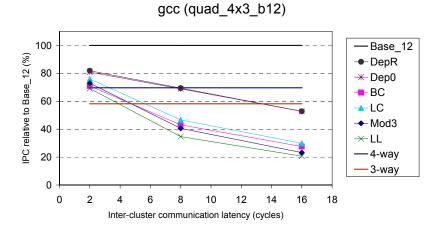

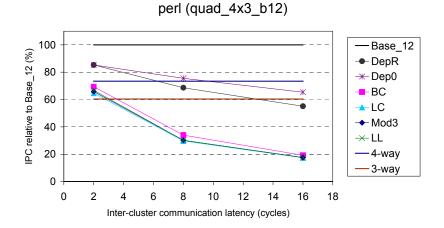

| Figure 6-15: Relative performance of conventional steering on quad_4x3_b12, with        |      |

| respect to Base 12, for gcc.                                                            | . 52 |

| Figure 6-16: Relative performance of conventional steering on quad_4x3_b12, with        |      |

| respect to Base_12, for <i>perl</i> .                                                   | . 52 |

|                                                                                         |      |

| Figure 6-17: Relative performance of conventional steering on quad_4x3_b12, with                      |

|-------------------------------------------------------------------------------------------------------|

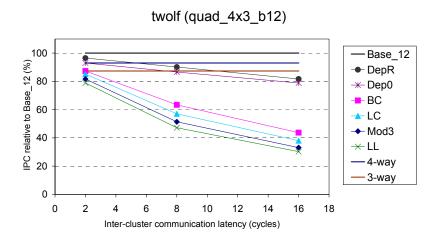

| respect to Base_12, for <i>twolf</i> 53                                                               |

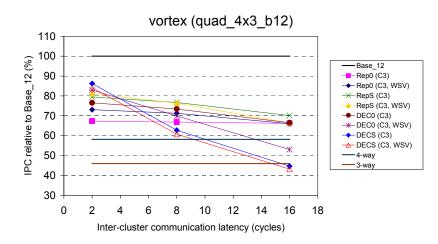

| Figure 6-18: Relative performance of conventional steering on quad_4x3_b12, with                      |

| respect to Base_12, for <i>vortex</i>                                                                 |

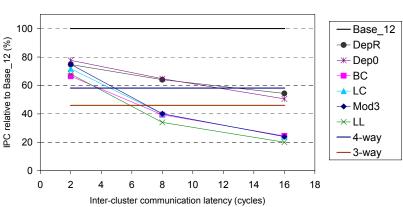

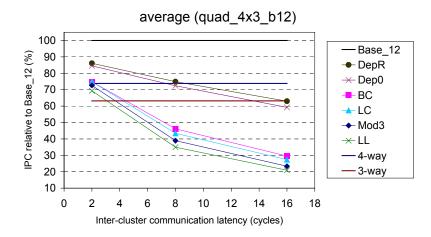

| Figure 6-19: Relative performance of conventional steering on quad_4x3_b12, with                      |

| respect to Base_12. Results are averaged across five benchmarks                                       |

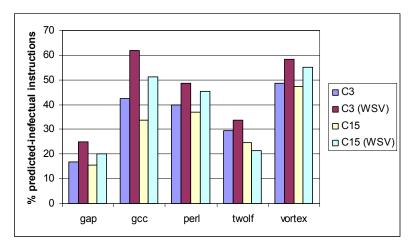

| Figure 6-20: Percentage of predicted-ineffectual instructions                                         |

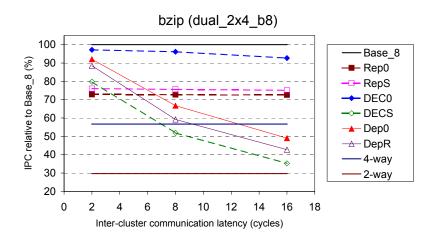

| Figure 6-21: Relative performance of slipstream-based steering (confidence threshold of               |

| 15 and no WSV) and dependence-based steering on dual_2x4_b8, with respect to                          |

| Base_8, for <i>bzip</i>                                                                               |

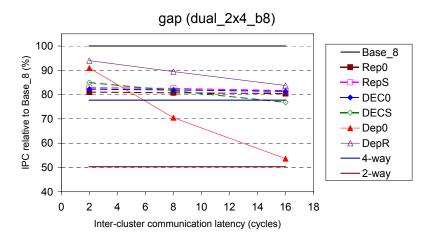

| Figure 6-22: Relative performance of slipstream-based steering (confidence threshold of               |

| 15 and no WSV) and dependence-based steering on dual_2x4_b8, with respect to                          |

| Base_8, for <i>gap</i>                                                                                |

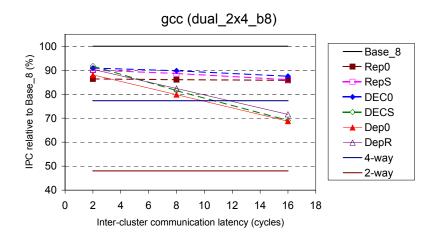

| Figure 6-23: Relative performance of slipstream-based steering (confidence threshold of               |

| 15 and no WSV) and dependence-based steering on dual_2x4_b8, with respect to                          |

| Base_8, for <i>gcc</i>                                                                                |

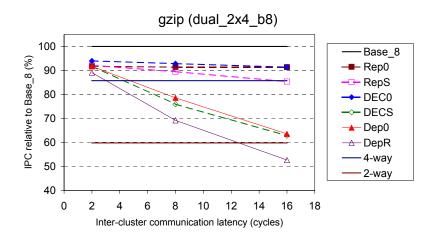

| Figure 6-24: Relative performance of slipstream-based steering (confidence threshold of               |

| 15 and no WSV) and dependence-based steering on dual_2x4_b8, with respect to                          |

| Base_8, for <i>gzip</i>                                                                               |

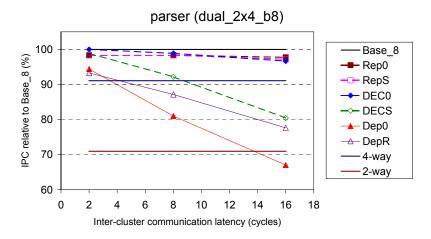

| Figure 6-25: Relative performance of slipstream-based steering (confidence threshold of               |

| 15 and no WSV) and dependence-based steering on dual_2x4_b8, with respect to                          |

| Base_8, for <i>parser</i> 61                                                                          |

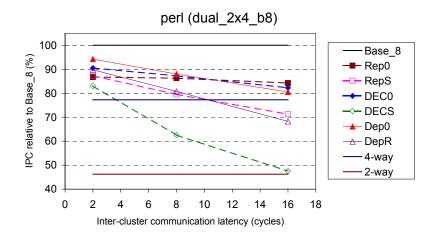

| Figure 6-26: Relative performance of slipstream-based steering (confidence threshold of               |

| 15 and no WSV) and dependence-based steering on dual_2x4_b8, with respect to                          |

| Base 8, for <i>perl</i>                                                                               |

| Figure $6-\overline{27}$ : Relative performance of slipstream-based steering (confidence threshold of |

| 15 and no WSV) and dependence-based steering on dual 2x4 b8, with respect to                          |

| Base_8, for <i>twolf</i>                                                                              |

| Figure 6-28: Relative performance of slipstream-based steering (confidence threshold of               |

| 15 and no WSV) and dependence-based steering on dual_2x4_b8, with respect to                          |

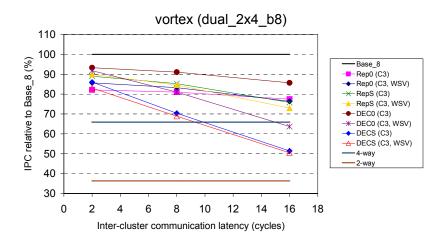

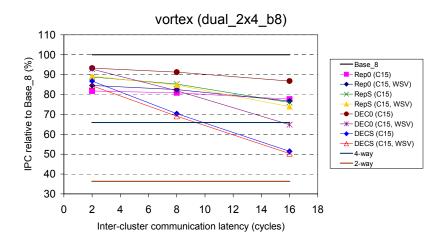

| Base 8, for <i>vortex</i>                                                                             |

| Figure $6-\overline{29}$ : Relative performance of slipstream-based steering (confidence threshold of |

| 15 and no WSV) and dependence-based steering on dual_2x4_b8, with respect to                          |

| Base 8, for <i>vpr</i>                                                                                |

| Figure $6-\overline{30}$ : Relative performance of slipstream-based steering (confidence threshold of |

| 15 and no WSV) and dependence-based steering on dual_2x4_b8, with respect to                          |

| Base 8. Results are averaged across all benchmarks                                                    |

| Figure 6-31: IPC improvement of slipstream-based steering (confidence threshold of 15                 |

| and no WSV) with respect to dependence-based steering on dual_2x4_b8. Results                         |

| are averaged across all benchmarks                                                                    |

| Figure 6-32: Relative performance of slipstream-based steering (confidence threshold of               |

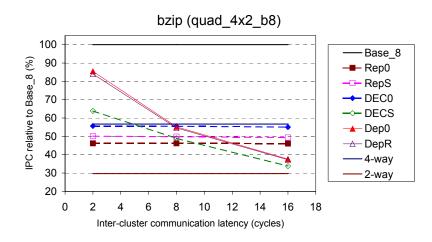

| 15 and no WSV) and dependence-based steering on quad_4x2_b8, with respect to                          |

| Base 8, for <i>bzip</i>                                                                               |

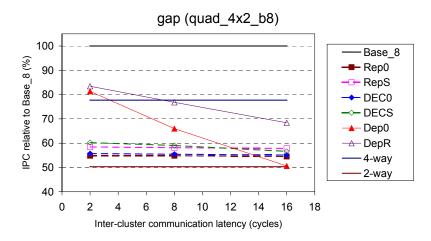

| Figure 6-33: Relative performance of slipstream-based steering (confidence threshold of               |

| 15 and no WSV) and dependence-based steering on quad_4x2_b8, with respect to                          |

| Base_8, for <i>gap</i>                                                                                |

|                                                                                                       |

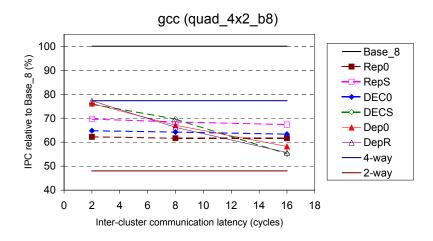

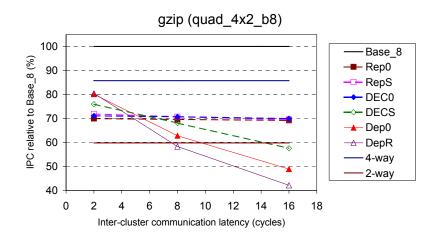

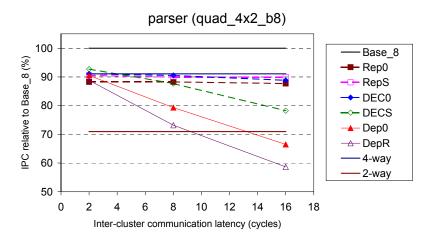

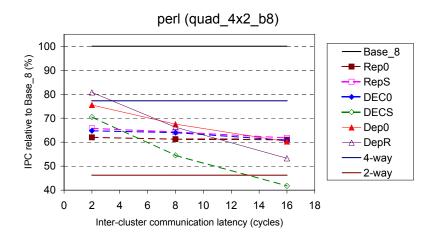

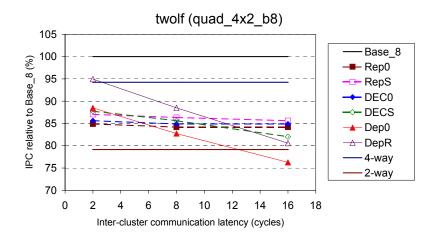

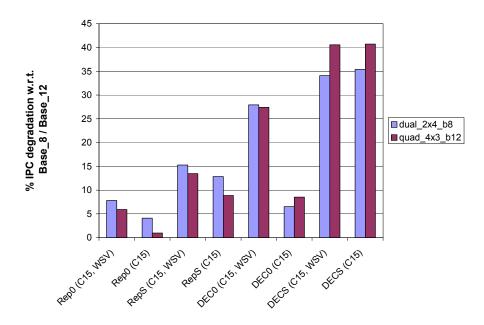

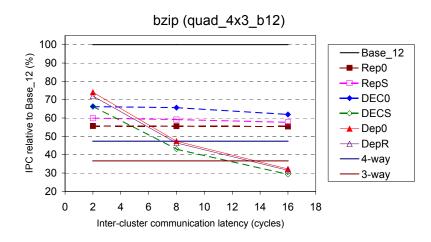

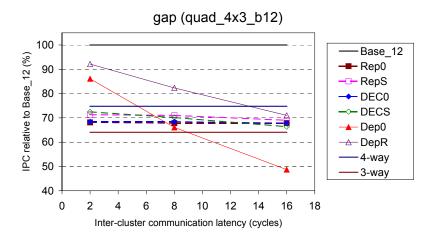

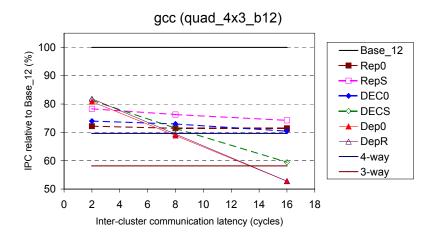

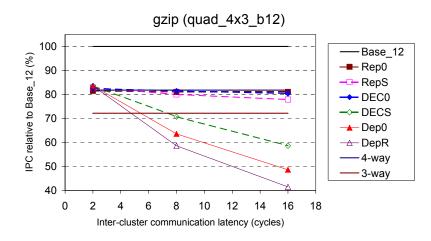

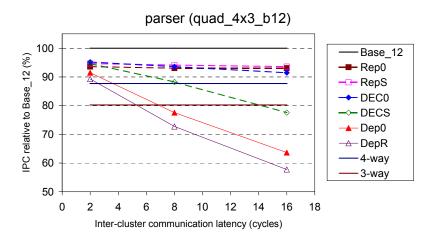

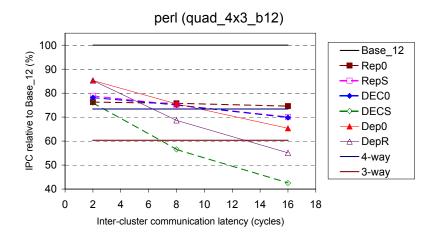

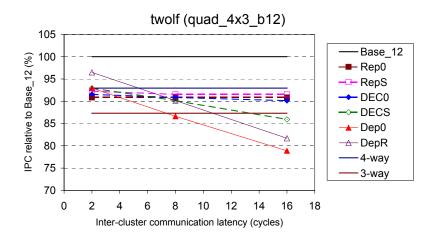

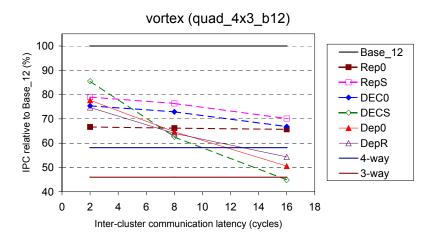

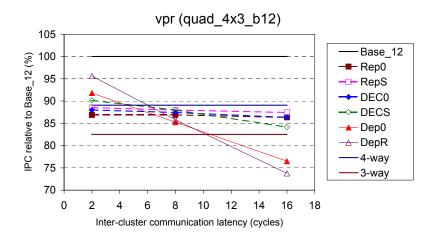

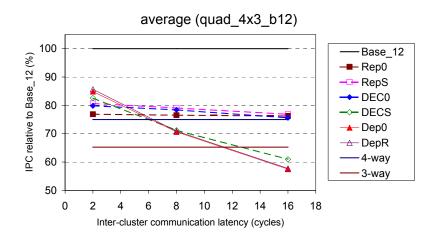

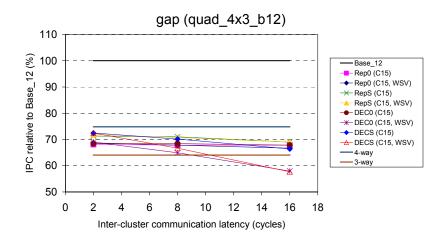

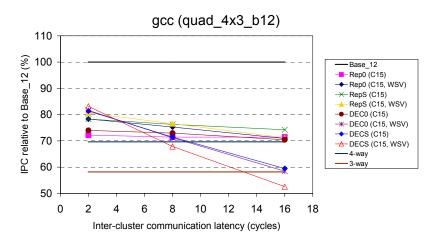

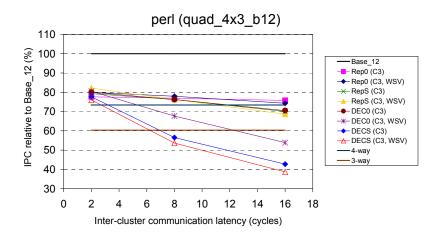

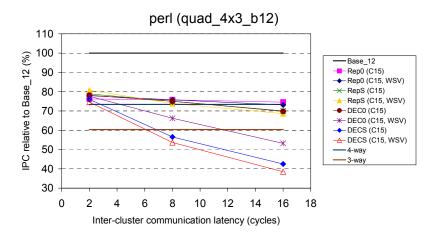

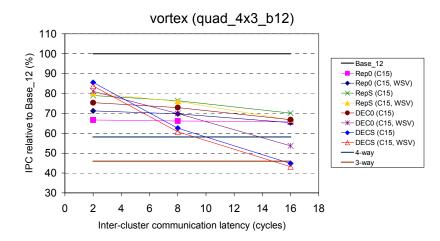

Figure 6-34: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad  $4x^2$  b8, with respect to Figure 6-35: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad  $4x^2$  b8, with respect to Figure 6-36: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad 4x2 b8, with respect to Figure 6-37: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad 4x2 b8, with respect to Figure 6-38: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad 4x2 b8, with respect to Figure 6-39: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad  $4x^2$  b8, with respect to Figure 6-40: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad 4x2 b8, with respect to Figure 6-41: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad  $4x^2$  b8, with respect to Figure 6-42: IPC improvement of slipstream-based steering (confidence threshold of 15 and no WSV) with respect to dependence-based steering on quad  $4x^2$  b8. Results Figure 6-43: Relative performance degradation of slipstream-based algorithms for Figure 6-44: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad 4x3 b12, with respect to Figure 6-45: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad 4x3 b12, with respect to Figure 6-46: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad 4x3 b12, with respect to Figure 6-47: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad 4x3 b12, with respect to Figure 6-48: Relative performance of slipstream-based steering (confidence threshold of 15 and no WSV) and dependence-based steering on quad 4x3 b12, with respect to

| Figure 6-49: Relative performance of slipstream-based steering (confidence threshold of |

|-----------------------------------------------------------------------------------------|

| 15 and no WSV) and dependence-based steering on quad_4x3_b12, with respect to           |

| Base_12, for <i>perl</i>                                                                |

| Figure 6-50: Relative performance of slipstream-based steering (confidence threshold of |

| 15 and no WSV) and dependence-based steering on quad_4x3_b12, with respect to           |

| Base_12, for <i>twolf</i> 75                                                            |

| Figure 6-51: Relative performance of slipstream-based steering (confidence threshold of |

| 15 and no WSV) and dependence-based steering on quad_4x3_b12, with respect to           |

| Base_12, for <i>vortex</i>                                                              |

| Figure 6-52: Relative performance of slipstream-based steering (confidence threshold of |

| 15 and no WSV) and dependence-based steering on quad_4x3_b12, with respect to           |

| Base_12, for <i>vpr</i> 75                                                              |

| Figure 6-53: Relative performance of slipstream-based steering (confidence threshold of |

| 15 and no WSV) and dependence-based steering on quad_4x3_b12, with respect to           |

| Base_12. Results are averaged across all benchmarks                                     |

| Figure 6-54: IPC improvement of slipstream-based steering (confidence threshold of 15   |

| and no WSV) with respect to dependence-based steering on quad_4x3_b12. Results          |

| are averaged across all benchmarks                                                      |

| Figure A-1: Relative performance of slipstream-based steering (confidence threshold of  |

|-----------------------------------------------------------------------------------------|

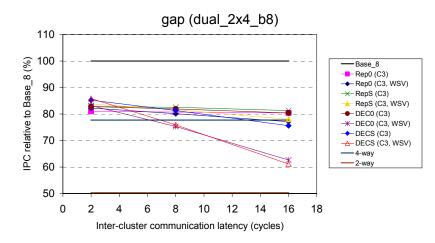

| 3) on dual_2x4_b8, with respect to Base_8, for <i>gap</i>                               |

| Figure A-2: Relative performance of slipstream-based steering (confidence threshold of  |

| 15) on dual_2x4_b8, with respect to Base_8, for <i>gap</i>                              |

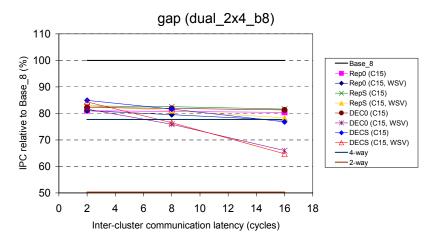

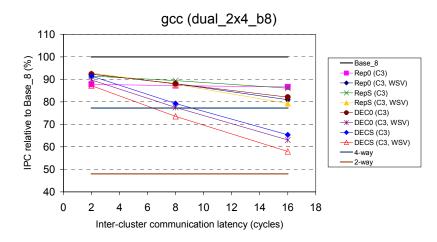

| Figure A-3: Relative performance of slipstream-based steering (confidence threshold of  |

| 3) on dual_2x4_b8, with respect to Base_8, for gcc                                      |

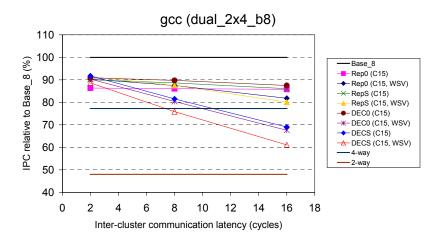

| Figure A-4: Relative performance of slipstream-based steering (confidence threshold of  |

| 15) on dual_2x4_b8, with respect to Base_8, for gcc                                     |

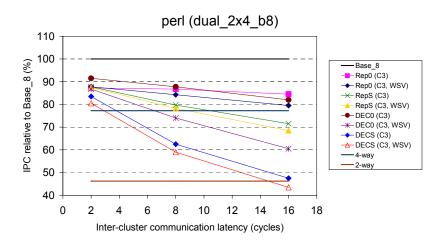

| Figure A-5: Relative performance of slipstream-based steering (confidence threshold of  |

| 3) on dual_2x4_b8, with respect to Base_8, for <i>perl</i>                              |

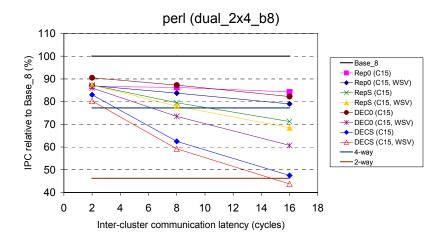

| Figure A-6: Relative performance of slipstream-based steering (confidence threshold of  |

| 15) on dual_2x4_b8, with respect to Base_8, for <i>perl</i>                             |

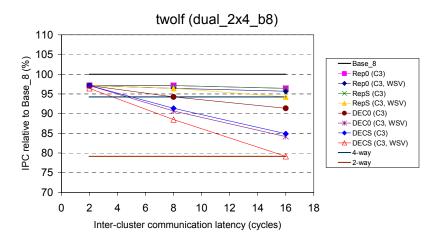

| Figure A-7: Relative performance of slipstream-based steering (confidence threshold of  |

| 3) on dual_2x4_b8, with respect to Base_8, for <i>twolf</i>                             |

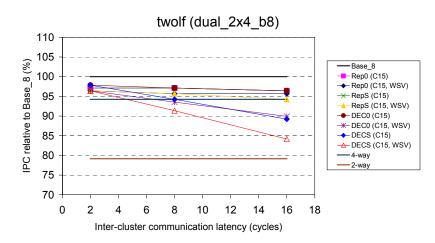

| Figure A-8: Relative performance of slipstream-based steering (confidence threshold of  |

| 15) on dual_2x4_b8, with respect to Base_8, for <i>twolf</i>                            |

| Figure A-9: Relative performance of slipstream-based steering (confidence threshold of  |

| 3) on dual_2x4_b8, with respect to Base_8, for <i>vortex</i>                            |

| Figure A-10: Relative performance of slipstream-based steering (confidence threshold of |

| 15) on dual_2x4_b8, with respect to Base_8, for <i>vortex</i>                           |

| Figure A-11: Relative performance of slipstream-based steering (confidence threshold of |

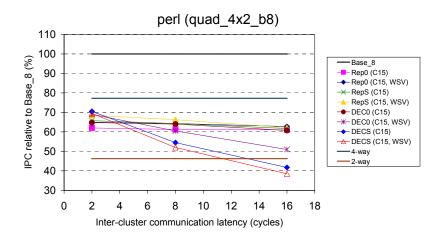

| 15) on quad_4x2_b8, with respect to Base_8, for <i>perl</i>                             |

| Figure A-12: Relative performance of slipstream-based steering (confidence threshold of |

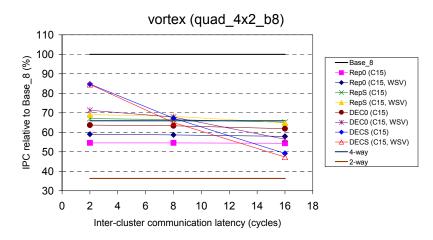

| 15) on quad_4x2_b8, with respect to Base_8, for <i>vortex</i>                           |

| Figure A-13: Relative performance of slipstream-based steering (confidence threshold of |

| 15) on quad_4x3_b12, with respect to Base_12, for gap                                   |

| Figure A-14: Relative performance of slipstream-based steering (confidence threshold of | of |

|-----------------------------------------------------------------------------------------|----|

| 15) on quad_4x3_b12, with respect to Base_12, for gcc.                                  | 94 |

| Figure A-15: Relative performance of slipstream-based steering (confidence threshold of | of |

| 3) on quad_4x3_b12, with respect to Base_12, for <i>perl</i>                            | 95 |

| Figure A-16: Relative performance of slipstream-based steering (confidence threshold of | of |

| 15) on quad_4x3_b12, with respect to Base_12, for <i>perl</i>                           | 95 |

| Figure A-17: Relative performance of slipstream-based steering (confidence threshold of | of |

| 3) on quad_4x3_b12, with respect to Base_12, for <i>vortex</i> .                        | 95 |

| Figure A-18: Relative performance of slipstream-based steering (confidence threshold of | of |

| 15) on quad_4x3_b12, with respect to Base_12, for <i>vortex</i> .                       | 96 |

## List of Tables

| Table 2-1: Comparison of hardware resources between a base superscalar pro | ocessor and a |

|----------------------------------------------------------------------------|---------------|

| quad-clustered processor                                                   |               |

| Table 5-1: Microarchitecture configuration.                                |               |

| Table 5-2: Benchmarks and input data sets.                                 |               |

| Table 6-1: IPC for 8-issue and 12-issue non-clustered processors           |               |

## **1** Introduction

Microarchitects attempt to exploit higher levels of instruction-level parallelism (ILP) by developing processors with larger instruction windows and higher peak issue rates. Studies have shown that it is not possible to increase processor complexity without adversely affecting cycle time [2][18]. To harvest increasing levels of ILP while maintaining a fast clock, clustered microarchitectures have been proposed. A clustered microarchitecture breaks the monolithic execution window of a conventional superscalar processor into multiple smaller windows, called clusters. Each cluster contains a relatively small issue queue, a copy of the register file, a small number of dedicated function units, and short (i.e., fast) bypasses among its function units. Effectively, each cluster is a small-scale superscalar processor. The efficiency of individual clusters (less complex issue logic, fast local bypasses, fewer register file read ports, etc.) allows the clustered microarchitecture to be clocked faster than a monolithic microarchitecture. Because of its significant advantages, clustering has already been implemented in the Alpha 21264 [13].

However, the fast clock enabled by clustering comes at the cost of multiple cycles to communicate values among clusters. If producer and consumer instructions are routed to different clusters, the execution of consumer instructions will be delayed due to *intercluster communication*. Thus, performance in terms of instructions executed per cycle (IPC) is significantly affected by how instructions are steered, i.e., how instructions are assigned to clusters. Various steering schemes have been proposed. Many of these are static (compiler-based) [9][17], while others are dynamic (based on run-time decisions) [4][6][7]. More recent steering approaches are based on critical-path prediction [10][30], the idea being that the execution of instructions on the critical path should not be delayed by global communication.

Instructions that constrain the execution time of a program constitute its critical path. To improve processor performance, the execution of critical-path instructions has to be optimized. In the case of a processor with a clustered microarchitecture, this implies that resource bottlenecks (e.g., limited function units in a cluster) and inter-cluster communication latency must have minimum impact on the execution of critical-path instructions.

This thesis proposes exploiting the distinction between effectual and ineffectual instructions, originally defined in the context of slipstream processors [14][20][21][24][28], in the context of clustered microarchitectures. The key idea put forth in the slipstream paradigm is that only some of the instructions in the dynamic instruction stream are needed for the correct forward progress of the program. These instructions are called *effectual* instructions. Instructions that are non-essential for correct forward progress are called *ineffectual* instructions. Ineffectual instructions include unreferenced writes, non-modifying writes, and highly predictable branches (and all of the computation chains feeding these instructions). We observe that ineffectual instructions are by definition not critical. Their outcomes are not needed, hence their completion does not need to be timely.

2

- *Unreferenced writes*: These instructions produce values that are never consumed.

- Non-modifying writes: These instructions do not change machine state and so

effectual dependent instructions are not truly dependent on them.

- *Correctly-predicted branches*: Since the predictions are correct, verification can be deferred without penalty (other than tying up rename checkpoints).

We conclude that the effectual component of the program is critical and the ineffectual component is not, and this distinction should shape the way in which instructions are assigned to clusters on a clustered microarchitecture.

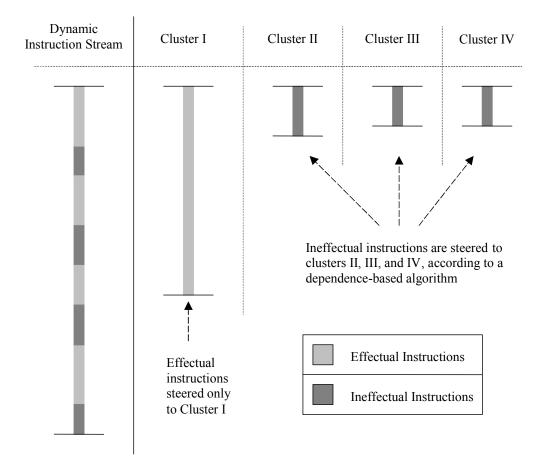

The chief performance limiter of a clustered microarchitecture is inter-cluster communication between instructions. Specifically, inter-cluster communication between critical-path instructions is the most harmful. The slipstream paradigm identifies criticalpath instructions in the form of effectual instructions. We propose eliminating virtually all inter-cluster communication among effectual instructions, simply by ensuring that the entire effectual component of the program executes within a cluster. We propose two alternative execution models that achieve this.

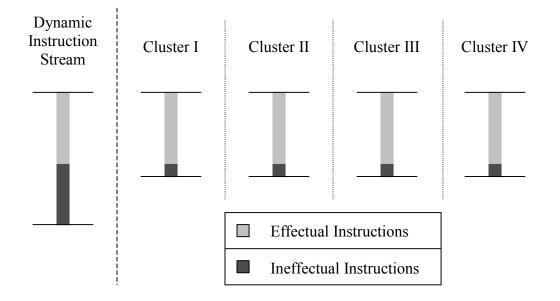

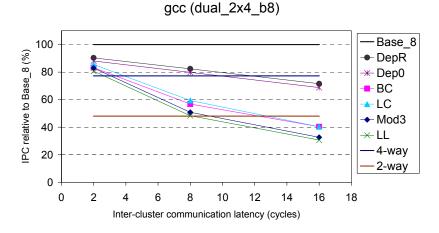

In the first model (called the *replication model*), the effectual program component (called the A-stream in slipstream processors [20]) is replicated and executed on all clusters. Ineffectual instructions are not replicated, i.e., they are executed in a distributed manner on all clusters. Consider the quad-cluster configuration shown in Figure 1-1. The dynamic instruction stream can be divided into an effectual

component and an ineffectual component. A full copy of the effectual component is executed on each cluster, whereas ineffectual instructions are distributed among the clusters.

Figure 1-1: Replication model of instruction execution in a clustered microarchitecture.

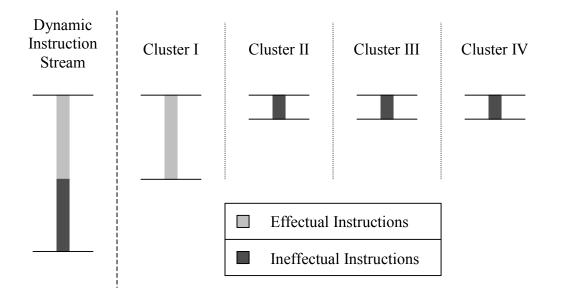

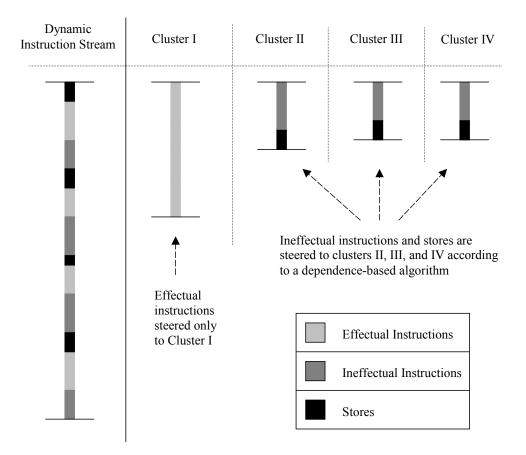

In the second model (called the *dedicated-cluster model*), a single copy of the effectual program component is executed on a dedicated cluster (i.e., no replication). Ineffectual instructions are executed in a distributed manner on all other clusters. From Figure 1-2, it can be seen that the effectual component of the dynamic instruction stream is executed only on cluster I, while ineffectual instructions are steered to clusters II, III, and IV.

Figure 1-2: Dedicated-cluster model of instruction execution in a clustered microarchitecture.

#### **1.1 Contributions**

This thesis proposes methods for minimizing inter-cluster communication between effectual instructions, virtually desensitizing the performance of a clustered microarchitecture to inter-cluster communication latency. The contributions of this thesis are as follows.

• A clustered microarchitecture has been developed that incorporates slipstream components for distinguishing effectual and ineffectual instructions. The rename stage is enhanced with conventional steering heuristics and new heuristics, including assigning the same instruction to multiple clusters (replication) according to various execution models. A key innovation is leveraging the

existing renaming/register file mechanisms for supporting the new execution models transparently.

• Four new algorithms (two based on the replication model and two based on the dedicated-cluster model) for instruction execution in a clustered microarchitecture are developed.

*Replication of effectual component*: A copy of the effectual program component is executed on each of the clusters. Thus, virtually no inter-cluster communication takes place between effectual instructions. The execution of ineffectual instructions is distributed across all clusters as the delay experienced in their execution can be tolerated.

*Replication of effectual component with store distribution*: The first algorithm puts extra pressure on the limited issue bandwidth of a cluster. To ease this pressure, the algorithm is slightly modified. Effectual stores are distributed instead of replicated, like ineffectual instructions. The rationale is that effectual stores are potentially more latency-tolerant than register-writing instructions, due to typically longer separation between stores and loads as compared to producers and consumers of register values. Issue bandwidth is freed within each cluster because each cluster no longer executes all effectual stores (effectual stores, like ineffectual instructions, are shared equally among all clusters).

*Dedicated-cluster for effectual component*: The effectual program component is executed on a single dedicated cluster called the *effectual cluster*. Ineffectual instructions are steered to clusters other than the effectual cluster. No inter-cluster communication exists between effectual instructions as they are executed on a single cluster.

Dedicated-cluster for effectual component with store distribution: In the previous algorithm, a large number of instructions are executed on the effectual cluster as compared to the number of instructions executed on each of the other clusters. Off-loading effectual stores to other clusters reduces demand on the effectual cluster and does not increase inter-cluster register communication. All effectual instructions except effectual stores are executed on a single cluster, while effectual stores and all ineffectual instructions are steered to the remaining clusters. The speedup gained by freeing execution resources on the effectual cluster compensates for the increase in inter-cluster communication between effectual stores and loads. This is especially beneficial in the case of low inter-cluster bypass latencies, where execution bandwidth, not communication, is the bottleneck.

• We study the effect of increasing inter-cluster communication latency on the performance of various steering heuristics for dual-cluster and quad-cluster configurations. To the best of our knowledge, no other research considers the impact of more than two cycles of inter-cluster communication latency.

7

(However, Aggarwal and Franklin [1] indirectly observed the effect of increasing inter-cluster communication latency by increasing the number of clusters.) We are interested in the impact of ramping up the clock rate of each cluster to the point where inter-cluster communication is in the tens-of-cycles regime. This scenario is effectively a distributed system on a single chip.

• We evaluate slipstream-related parameters in the design space of slipstream-based clustered microarchitectures. We vary instruction-removal confidence threshold and instruction-removal criteria.

#### **1.2** Organization of the Thesis

Chapter 2 gives an overview of clustered microarchitectures and conventional steering heuristics. Chapter 3 gives an overview of slipstream components that separate effectual and ineffectual instructions. In Chapter 4, slipstream-based steering models are proposed and explained. The simulation methodology and benchmarks are described in Chapter 5. Chapter 6 presents the experimental results. Related work is discussed in Chapter 7. Chapter 8 summarizes the thesis and proposes future work.

## **2 Processors with a Clustered Microarchitecture**

The amount of instruction-level parallelism (ILP) that can be extracted from a program plays a major role in the performance of a superscalar processor. Larger instruction windows combined with higher peak issue rates and more function units can exploit large amounts of ILP. Studies have shown that large instruction windows and high issue rates result in slower wakeup and select logic [2][18]. Also, larger register files and more function units result in slower bypasses. Therefore, it is not possible to build large monolithic instruction windows without adversely affecting the cycle time of a processor.

In order to harvest increasing levels of ILP while maintaining a fast clock, clustered microarchitectures have been proposed. A clustered microarchitecture divides the monolithic execution window of a conventional superscalar processor into multiple smaller windows called clusters. A cluster consists of a relatively small instruction window, a copy of the register file, a small number of dedicated function units, and short bypasses among its function units called *intra-cluster bypasses*. Intra-cluster bypasses are fast because they span only a few function units. A global bypass bus called the *inter-cluster bypass bus* interconnects all the clusters in the processor. The longer inter-cluster bypasses are slow because they span all clusters.

The method by which instructions are assigned to a specific cluster for execution is called *steering*. The pipeline stage that performs steering depends on the type of clustered microarchitecture. For the type of clustered microarchitecture described earlier, the dispatch stage performs steering. This has been called *dispatch-driven* instruction steering by Parlacharla and Smith [18]. Dispatch-driven steering results in a highly-efficient design for individual clusters. The smaller instruction window and moderate issue bandwidth imply less complex (i.e., fast) wakeup and select logic. Fewer function units and a smaller register file (due to fewer read ports) enable the use of shorter (i.e., faster) bypasses within a cluster. Thus, a clustered microarchitecture can be clocked faster than a monolithic microarchitecture.

A second form of clustered microarchitecture uses a monolithic instruction window that issues instructions to multiple clusters. In this case, a cluster only has a copy of the register file, a small number of dedicated function units, and short bypasses among its function units. As before, inter-cluster bypasses connect the clusters and are slower than the fast intra-cluster bypasses. In this form of clustered microarchitecture, an instruction resides in the monolithic issue queue and is assigned to a cluster only when it becomes ready to issue. Thus, instruction steering is performed in the issue stage. This approach has been called *execution-driven* instruction steering by Parlacharla and Smith [18]. This form of clustered microarchitecture has been implemented in the integer pipeline of the Alpha 21264 [13]. The integer pipeline has a single issue queue with two clusters. Each integer cluster consists of a copy of the integer register file and an equal number of integer function units. A value produced in a cluster is communicated to consumers in the same cluster, in the same cycle the value is produced. However, the value takes an extra cycle to be communicated to consumers in the other cluster.

Execution-driven steering tends to be more effective than dispatch-driven steering because it defers steering until a more informed decision can be made. However, this approach uses a large instruction window and is therefore less complexity-effective. Also, steering logic is added to the issue stage, making it even more complex. Therefore, the dispatch-driven approach is the better method in terms of efficiency.

#### 2.1 Clustered Microarchitecture

In this thesis, we will consider a clustered microarchitecture that utilizes dispatchdriven steering. Instructions are steered to clusters at the time of dispatch. Consequently, instructions issue and execute within the cluster to which they are steered, as they would on a small-scale superscalar processor. A value produced within a cluster is quickly bypassed to consumers in the same cluster, via the intra-cluster bypasses. Thus, producers and consumers execute in consecutive cycles if they are in the same cluster. All values produced within a cluster are also communicated to the other clusters. However, values produced in a cluster are available to consumers in another cluster only after a certain delay called the *inter-cluster communication latency*. This delay depends on the number of clusters and the size of the clusters.

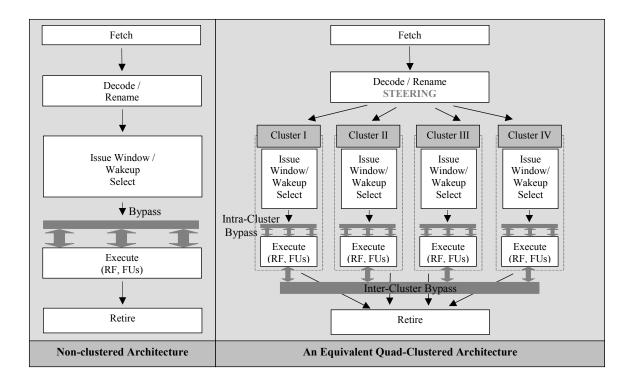

As we move from a centralized microarchitecture to a clustered microarchitecture, several changes are needed. The salient features of a clustered microarchitecture are highlighted by comparing a quad-clustered configuration to a non-clustered configuration, in Figure 2-1.

11

Figure 2-1: Comparison between a non-clustered microarchitecture and a quad-clustered microarchitecture.

Note that the execution resources of the monolithic microarchitecture are divided equally among all clusters. From the figure, the following observations can be made.

- Each cluster has a copy of the physical register file. A value produced within a cluster is written into its copy of the register file, and all other copies. However, it takes longer for the value to propagate to other copies of the register file (i.e., register files in other clusters), and it is dictated by the inter-cluster bypass latency. The crucial advantage of replicating the register file is that the number of read ports for each copy of the register file is far fewer than the number of read ports for the register file of a monolithic configuration. The reason is that fewer instructions issue each cycle within a cluster.

- The issue window, issue bandwidth, and function units of the monolithic configuration are divided equally among all clusters.

- An intra-cluster bypass bus is used to communicate values within a cluster and an inter-cluster bypass bus is added to connect all clusters. The intra-cluster bypasses are much faster than the inter-cluster bypass.

- To ensure that store-load dependences are observed, the memory disambiguation unit is replicated, i.e., all clusters maintain a copy of the load/store queue. Stores broadcast their addresses and values to all clusters, incurring the penalty of intercluster communication latency. The store addresses and values are used by each cluster to detect memory dependences and perform store-load forwarding as needed.

- There is no change to the in-order front-end (fetch unit, decode, and rename unit) and in-order back-end (retirement unit). The fetch, dispatch, and retire stages remain centralized. Only the out-of-order execution window is distributed. The only modification is that steering functionality is added to the dispatch stage.

Table 2-1 summarizes how the various resources of a non-clustered microarchitecture change after distributing them among clusters in a quad-clustered configuration. The first column in the table shows the hardware resources. The second column characterizes the resources for the monolithic configuration. The third column characterizes the resources for the quad-cluster configuration. From the table, the following observations can be made regarding a clustered microarchitecture.

• The fetch and dispatch stages are common to all clusters, hence the fetch bandwidth and dispatch bandwidth are not distributed. Likewise, the retirement stage is common to all clusters.

13

- The organization of the execution window is effectively transparent to renaming and retirement, hence there is only one architectural map table, rename map table, and free list, as usual.

- The issue bandwidth, cache ports, instruction queue, and function units of the monolithic microarchitecture are divided equally among the four clusters.

- The register file is replicated, one copy per cluster. However, the number of read ports to each cluster register file is reduced with respect to the monolithic register file, since each cluster register file only needs to support reads from instructions within the cluster. The number of write ports to each cluster register file is not reduced with respect to the monolithic register file because all values are written into each cluster register file.

- The load/store queue is replicated, one copy per cluster, as described earlier.

| Hardware Resource       | Base Superscalar | Quad – Cluster        |

|-------------------------|------------------|-----------------------|

| Fetch bandwidth         | 8                | 8 (common to all)     |

| Dispatch bandwidth      | 8                | 8 (common to all)     |

| Active list size        | 128              | 128 (common to all)   |

| Free list size          | 128              | 128 (common to all)   |

| Rename map table        | 1                | 1 (common to all)     |

| Architectural map table | 1                | 1 (common to all)     |

| Issue bandwidth         | 8                | 2 per cluster         |

| Cache ports             | 4                | 1 per cluster         |

| Issue queue             | 128              | <i>32 per cluster</i> |

| Registers               | 195              | 195 per cluster       |

| Register read ports     | 16               | 4 per cluster         |

| Register write ports    | 8                | 8 per cluster         |

| Load / store unit       | 1                | l per cluster         |

| Retire bandwidth        | 8                | 8 (common to all)     |

Table 2-1: Comparison of hardware resources between a base superscalar processor and a quadclustered processor.

Each cluster has a copy of the physical register file. This not only provides fast local access, but it also reduces the number of read ports to the register file. The number of read ports affects the size and hence the speed of the register file. This gives the clustered microarchitecture an edge over the non-clustered microarchitecture. The number of read and write ports are calculated in the following two sections.

#### 2.1.1 Number of write ports to a cluster register file

An instruction can produce only one value. Thus, a single write port is needed per instruction per cycle. Therefore, the maximum number of write ports (WP) needed for a monolithic microarchitecture is as follows.

$WP_{monolithic} = IW$  Equation 2-1

The number of writes that can occur simultaneously within a cluster is equal to the aggregate issue width of the clustered microarchitecture. The reason is that all values have to be written in each cluster register file, even those produced by other clusters. Thus, the number of write ports is determined by the aggregate issue width of the clustered microarchitecture.

$WP_{cluster} = n * CIW$  Equation 2-2

Above, n is the number of clusters and CIW is the cluster issue width.

The aggregate issue width of the clustered microarchitecture equals the total issue width of the monolithic microarchitecture, therefore:

n \* CIW = IW ..... Equation 2-3

| $WP_{cluster} = IW$              | <br>Equation 2-4 |

|----------------------------------|------------------|

| $WP_{cluster} = WP_{monolithic}$ | <br>Equation 2-5 |

Thus, the number of write ports to the cluster register file is equal to the number of write ports to the monolithic register file.

#### 2.1.2 Number of read ports to a cluster register file

In general, the number of read ports to a register file is determined by the issue width (IW) of the processor. An instruction can have a maximum of two source operands. Hence, two reads are performed at the same time for one instruction, which implies that two read ports are needed per instruction per cycle. Therefore, the maximum number of read ports (RP) needed for a monolithic microarchitecture is as follows.

$RP_{monolithic} = 2 * IW$  Equation 2-6

The number of instructions that can be issued per cycle within a cluster is the cluster issue width (CIW). The number of read ports to the cluster register file is determined by this cluster issue width, as follows.

| $RP_{cluster} = 2 * CIW$             | <br>Equation 2-7 |

|--------------------------------------|------------------|

| $RP_{cluster} = 2 * IW / n$          | <br>Equation 2-8 |

| $RP_{cluster} = RP_{monolithic} / n$ | <br>Equation 2-9 |

It can be seen that the number of read ports per cluster register file is reduced by a factor of n with respect to the monolithic register file, thereby reducing its complexity and improving the register access time. For the quad-cluster configuration shown,

$RP_{cluster} = \frac{1}{4} RP_{monolithic}$  Equation 2-10

#### 2.2 Bottlenecks in a Clustered Microarchitecture

The efficiency of various hardware resources enables a clustered microarchitecture to have a shorter clock period than a monolithic microarchitecture. However, clustered microarchitectures suffer from the following bottlenecks.

- Inter-Cluster Communication Latency: It takes multiple clock cycles to communicate values via the long inter-cluster bypasses. The execution of an instruction whose source operands are produced in another cluster is delayed due to the extra time it takes for values to be communicated via the inter-cluster bypass.

- *Smaller Cluster Issue Bandwidth*: There may be more instructions ready for issue on a cluster than can be issued in a cycle, while at the same time, there may be empty issue slots available in another cluster. This imbalance leads to issue bandwidth stalls on one cluster and under-utilization of resources on the other.

## 2.3 Steering Heuristics

Steering heuristics dictate the performance achieved by a clustered microarchitecture. Effective steering can reduce inter-cluster communication and optimize resource usage, whereas ineffective steering can cause significant performance degradation and negate the advantage that a clustered microarchitecture provides over a monolithic microarchitecture. Various steering heuristics have been proposed.

**Modulo**<sub>n</sub> (Mod3) [4]: A new cluster is selected every n instructions on the basis of a round-robin policy. For example, for Mod3 steering in a quad-cluster configuration, the first three instructions are assigned to cluster I, the next three to cluster II, and so on. This algorithm does not try to minimize inter-cluster communication but achieves a fairly good load balance via equal instruction distribution among clusters.

**Branch-Cut (BC)** [4]: Instructions are assigned to the same cluster until a branch is reached. Instructions after the branch are then assigned to a new cluster according to a round-robin policy. Therefore, instructions are steered on a basic block level. It has been observed that instructions within a basic block typically belong to the same dependence chain(s). Thus, forcing a possible dependent chain of instructions onto the same cluster would reduce inter-cluster communication and achieve a balanced distribution of instructions among the clusters.

**Load-Cut (LC)** [4]: Instructions are assigned to the same cluster until a load is reached. The load and instructions following the load are assigned to a new cluster according to a round-robin policy. Loads often begin a chain of dependent instructions. Thus, by changing the cluster on encountering a load, a possible dependent chain of instructions is steered to the same cluster and inter-cluster dependences are reduced accordingly. **Least-Loaded (LL)** [4]: This algorithm tries to balance the distribution of instructions among clusters. Every new instruction is assigned to the *least-loaded cluster*. The least loaded cluster is the cluster with the least number of instructions in its issue queue.

**Dependence-Based (Dep0)**: This steering heuristic was proposed by Canal et. al. [6]. An explicit attempt is made to minimize inter-cluster communication by steering consumer instructions to the same cluster as their producers. The information needed for steering is obtained during instruction decoding/renaming because register dependences have to be taken into consideration. The algorithm works as follows.

- If an instruction has no source operands, it is assigned to the least-loaded cluster.

- If an instruction has one source operand, it is assigned to the cluster where the source operand has been produced or will be produced.

- If an instruction has two source operands, and both are in the same cluster, then the instruction is assigned to that cluster. If the two source operands are produced in different clusters, then the instruction is assigned to the least-loaded cluster among the producer clusters.

**Readiness-Dependence-Based (DepR)**: This steering heuristic is very similar to the one proposed by Baniasadi et. al. [4]. Like the previous dependence-based scheme, this scheme also explicitly tries to minimize inter-cluster communication, but it takes the readiness of the source operands into account. A source operand is said to be *globally ready* if it is ready for consumption in all the clusters, and not just its producer cluster. The algorithm works as follows.

- If an instruction has no source operands, it is assigned to the least-loaded cluster.

- If an instruction has one source operand and that operand is globally ready, it is assigned to the least-loaded cluster. Otherwise, the instruction is steered to the cluster that produced or will produce the source operand.

- If an instruction has two source operands and both are globally ready, it is assigned to the least-loaded cluster. Otherwise, it is assigned to the cluster that produces the youngest source. The youngest source refers to the source operand whose producer is the closest to this instruction (consumer), in program order.

## **3** Slipstream Components used for Steering

The slipstream paradigm [20] proposes that only a fraction of the dynamic instruction stream is needed for a program to make correct forward progress. This component of the dynamic instruction stream is termed *effectual*. Many general-purpose programs contain a significant number of instruction sequences that either have no effect on the final outcome of a program or are highly predictable. Such instructions are called *ineffectual* instructions. Ineffectual instructions include unreferenced writes, non-modifying writes, highly-predictable branches, and computation chains leading up to them.

A slipstream processor runs two redundant copies of a program, one slightly ahead of the other, on a chip multiprocessor (CMP) or a simultaneous multithreading (SMT) processor. Ineffectual instructions are speculatively removed from the leading program, called the advanced stream (A-stream). The A-stream is sped up because it fetches and executes fewer instructions than the original program. All data and control outcomes from the A-stream are communicated to the trailing program, called the redundant stream (R-stream). The R-stream compares the communicated outcomes against its own outcomes. If a deviation is detected, the corrupted A-stream context is recovered from the R-stream context. This deviation is called an *IR-misprediction*. The R-stream also exploits the outcomes of the A-stream as accurate branch and value predictions. Thus, although the R-stream retires the same number of instructions as the original program, it fetches and executes much more efficiently. As a result, both program copies finish sooner than the original program.

Two slipstream components are needed for identifying ineffectual instructions.

- 1. The *instruction-removal predictor*, or *IR-predictor*, is essentially a branch predictor augmented for instruction removal. It generates the program counter (PC) for the next block of instructions to be fetched in the A-stream, similar to a conventional branch predictor. The IR-predictor also specifies a bit-vector that identifies ineffectual instructions within a fetch block.

- 2. The *instruction-removal detector*, or *IR-detector*, identifies past instructions which were not essential for the R-stream's correct forward progress. The IR-detector then conveys to the IR-predictor that these instructions can potentially be skipped in the A-stream, in the future. The IR-predictor removes the corresponding instructions from the A-stream after repeated indications by the IR-detector, i.e., after a certain confidence threshold has been reached.

### 3.1 IR-predictor

The IR-predictor is a conventional branch predictor augmented to keep track of instruction removal information. It is indexed like the *gshare* predictor[15], by XORing the PC with the global branch history bits. Each table entry contains the following information for a dynamic basic block.

- *Tag*: This is the start PC of the basic block and is used to determine whether the entry contains information for the block being fetched. A partial tag can be used to reduce the total storage, if predictor aliasing is negligible.

- *2-bit counter*: A 2-bit counter is used to predict the outcome of a basic block that ends with a conditional branch.

- *Confidence counters*: A resetting confidence counter [12] is provided for each instruction in the basic block. The counter corresponding to a particular instruction is incremented if the IR-detector identified that instruction to be ineffectual. Otherwise, the counter is reset to zero. Repeated indications by the IR-detector saturate the confidence counter, in which case the corresponding instruction is predicted to be ineffectual by the IR-predictor and removed from the A-stream when it is next encountered.

#### 3.2 IR-detector

The IR-detector consumes retired R-stream instructions and data. It then identifies instructions which were not essential for correct forward progress, in retrospect. The IR-detector watches for any of the following three triggering conditions for instruction removal.

- *Unreferenced writes*, i.e., a write followed by a write to the same location, with no intervening read.

- *Non-modifying writes*, i.e., a write that does not modify the value of a location.

- *Correctly-predicted branches.*

When any of the above conditions are observed, the corresponding instruction is selected for removal and this information is passed on to the IR-predictor. Additional ineffectual instructions are selected by a technique called *back-propagation*. Back-propagation detects computation chains that feed the instructions selected for removal based on the triggering conditions mentioned above. An instruction can be selected for removal if all of its dependent instructions are selected for removal. For example, once a branch is selected, the computation leading to that branch is no longer needed and can be selected for removal, if no other instructions depend on the computation.

## 3.3 Use of IR-detector/IR-predictor in Steering Mechanisms

For our purposes, the IR-detector and IR-predictor are used only as a means for identifying predicted-ineffectual instructions. That is, they are not actually used to remove instructions, since there is no separate A-stream thread.

The bit vector produced by the IR-predictor identifies ineffectual instructions and this is used by the steering mechanism directly, for distinguishing between effectual and ineffectual instructions.

## 4 Thesis Contribution: Slipstream-Based Steering

The goal of slipstream-based steering is to desensitize IPC performance to tens of cycles of inter-cluster communication latency. We conjecture that executing the effectual component entirely on a single cluster will achieve this goal while still effectively exploiting the parallel resources available in the clustered microarchitecture.

## 4.1 Replication of Effectual Component (Rep0)

We attempt to eliminate inter-cluster communication among effectual instructions by executing a copy of the effectual component on each of the clusters. On the other hand, the ineffectual component of the program is distributed (shared) among the clusters. Thus, the only potential inter-cluster communication is between ineffectual instructions in different clusters. Intra-cluster communication is guaranteed between (1) effectual producers and effectual consumers, and (2) effectual producers and ineffectual consumers. The latter aspect distinguishes the replication models described in this section and Section 4.2 from the non-replication models (dedicated-cluster models) described in Sections 4.3 and 4.4.

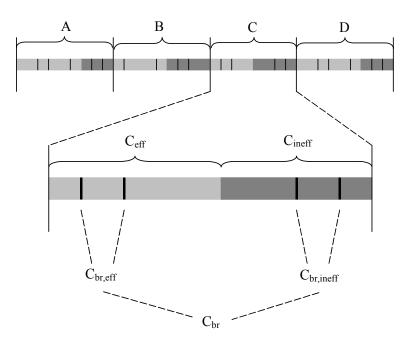

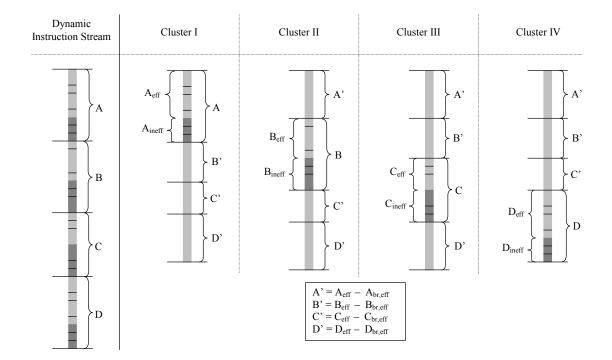

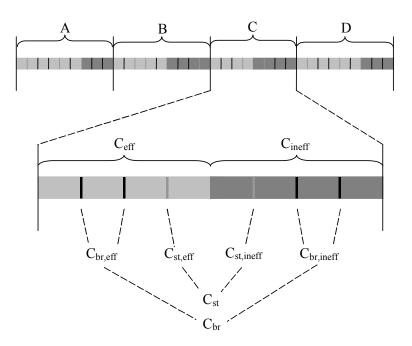

To manage the distribution of ineffectual instructions, the dynamic instruction stream is divided into traces. A trace consists of one or more basic blocks and is composed of both effectual and ineffectual instructions. This can be seen in Figure 4-1 (light gray = effectual, dark gray = ineffectual). A, B, C, and D are traces that are part of the dynamic instruction stream.  $C_{eff}$  is the predicted-effectual component and  $C_{ineff}$  is the predicted-ineffectual component of trace C. We use  $C_{br}$  to refer to all the branches in trace C. Branches can also be divided into predicted-effectual branches ( $C_{br,eff}$ ) and predicted-ineffectual branches ( $C_{br,ineff}$ ).

| $C = C_{eff} + C_{ineff}$            | <br>Equation 4-1 |

|--------------------------------------|------------------|

| $C_{br} = C_{br,eff} + C_{br,ineff}$ | <br>Equation 4-2 |

Dynamic Instruction Stream

Figure 4-1: A breakdown of the dynamic instruction stream.

We say that each trace is *owned* by a particular cluster. A new trace is assigned to a cluster in a round-robin manner. For an n-cluster configuration, each cluster owns one out of every n traces. All instructions in a trace are executed within the cluster that owns the trace. Therefore, predicted-effectual and predicted-ineffectual instructions of a trace are executed within the cluster which owns that trace. Only the predicted-effectual instructions of the trace are executed on clusters that do not own the trace. In this way, predicted-effectual instructions are replicated and predicted-ineffectual instructions are distributed equally among the clusters.

According to this policy, effectual branches are redundantly executed on all clusters, raising the question of how to resolve mispredicted branches. The first option is to exploit redundancy and thereby allow the earliest resolved branch to redirect the fetch unit. However, we found the complexity of managing multiple branches with a single rename checkpoint to be cumbersome. So, we instead implemented the second option, which is to steer effectual branches to only a single cluster, the one that owns the trace containing the branch. This also reduces contention for issue bandwidth within the clusters slightly. Note also that it does not increase inter-cluster communication.

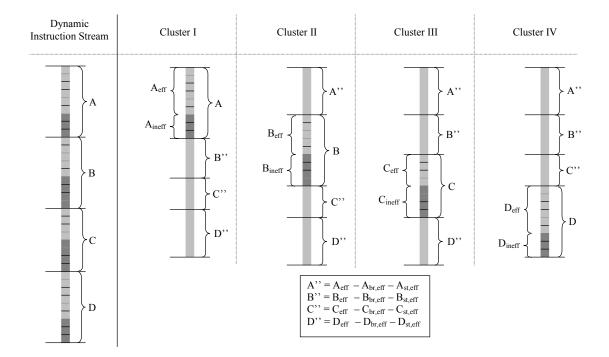

Figure 4-2 shows how this heuristic works for a quad-cluster configuration. A segment of the dynamic instruction stream is divided into four traces, A, B, C, and D. A' is the reduced version of trace A. For the quad-cluster configuration shown, cluster I owns trace A, cluster II owns trace B, cluster III owns trace C, and cluster IV owns trace D. Thus, a cluster owns one in every four traces. All instructions in trace A are executed on cluster I, but predicted-ineffectual instructions and branches of trace A are not executed on clusters II, III, and IV. In other words, predicted-effectual instructions minus predicted-effectual branches of trace A are executed on clusters II, III, and IV. The reduced version of trace A can therefore be represented as follows.

| $A' = A - A_{ineff} - A_{br,eff}$ |  | Equation 4-3 |

|-----------------------------------|--|--------------|

|-----------------------------------|--|--------------|

Since  $A = A_{eff} + A_{ineff}$ ,

$$A' = A_{eff} - A_{br,eff} \qquad \qquad \text{Equation 4-4}$$

The same logic can be applied to the other traces.

Figure 4-2: Replication of the effectual component.

#### 4.1.1 Implications of redundant execution

In a clustered microarchitecture, each cluster has a copy of the physical register file. While decoding and renaming an instruction, the logical destination register is mapped to the same physical register on all clusters. Using our steering algorithm, a predicted-effectual instruction is dispatched to each of the clusters for redundant execution. This does not require changes to the existing rename mechanism. All copies of an instruction will write their *identical* values to the same location in all the physical register files. Note that it is wasteful for effectual copies to broadcast their values to other clusters. We could eliminate communication for these redundant values, and thereby reduce register file write ports, reduce power consumption on inter-cluster bypasses, etc. This aspect is discussed in the future work section (Section 8.2).

As predicted-effectual instructions are executed redundantly on each of the clusters, it is possible that the result of a predicted-effectual instruction executed on cluster I is communicated to cluster II before cluster II's copy of the instruction has executed. In this case, dependent instructions in cluster II may issue/execute before the parent instruction executes in cluster II. Since the values produced by redundant instructions are identical, there is no problem with this scenario.

#### 4.1.2 Regarding memory disambiguation

In the base clustered microarchitecture, broadcast of store addresses and values to other clusters is delayed by the inter-cluster communication latency. This may make memory disambiguation a major bottleneck due to loads conservatively waiting for all prior store addresses. A solution is to use aggressive memory dependence speculation. It has been shown that memory dependence speculation is almost as accurate as oracle memory disambiguation [8][16]. In any case, our architecture is less sensitive to this problem since effectual stores and loads reside in the same cluster. There is still the problem of ineffectual stores delaying disambiguation of effectual loads in other clusters. Memory dependence speculation could very accurately predict that there are no dependences in this situation, since presumably effectual loads should not depend on ineffectual stores.

#### 4.1.3 Implication of IR-mispredictions

An instruction-removal misprediction, or IR-misprediction, occurs when an effectual instruction is incorrectly predicted as an ineffectual instruction [20]. In our context, this implies that an instruction that should have executed redundantly on each of the clusters is now executed on only one of the clusters. Thus, effectual instructions that depend on an IR-mispredicted-instruction in another cluster will have to wait for the value to be communicated via the inter-cluster bypass. Therefore, an IR-misprediction results in inter-cluster communication between effectual instructions.

## 4.1.4 Changes to the microarchitecture

Key changes that must be introduced in the microarchitecture for implementing this scheme are as follows.

- After fetching an instruction, it is dispatched to all clusters if it is predictedeffectual (except for predicted-effectual branches), or steered to one of the clusters (depending on the owner of the trace) if it is predicted-ineffectual or a predicted-effectual branch.

- Instruction dispatch is stalled if any of the cluster issue queues are full. This is only true for predicted-effectual instructions (except branches) since they must be replicated.

• A predicted-effectual instruction is retired only after all copies have completed execution on each of the clusters. In other words, multiple instances of an instruction are re-integrated into a single instance before retiring.

# 4.2 Replication of Effectual Component with Store Distribution (RepS)

We modify the algorithm in Section 4.1 to reduce contention for cluster issue bandwidth. Instead of replicating effectual stores, we distribute them just like ineffectual instructions, based on the fact that memory dependence distances are longer than register dependence distances. Therefore, all predicted-effectual instructions except predictedeffectual branches and predicted-effectual stores are replicated. This implies that no branches or stores are replicated.

Distributing effectual stores increases inter-cluster communication between effectual stores and loads. On the other hand, by not executing stores redundantly, resources are freed for executing the residual effectual component faster. The newlyexposed inter-cluster communication between effectual stores and loads may be offset by the speedup gained by freeing execution resources in each cluster.

Figure 4-3 shows a segment of the dynamic instruction stream with a breakdown of effectual and ineffectual instructions. In addition to the terms used in Figure 4-1, a few

more terms are introduced.  $C_{st}$  indicates all the stores in trace C,  $C_{st,eff}$  indicates the predicted-effectual stores, and  $C_{st,ineff}$  indicates the predicted-ineffectual stores.

Dynamic Instruction Stream

Figure 4-3: A breakdown of the dynamic instruction stream.

Consider the quad-cluster configuration shown in Figure 4-4. A segment of the dynamic instruction stream is divided into traces A, B, C, and D. A'' indicates the reduced version of a trace. As in the first algorithm, a cluster owns one in every four traces. Therefore, cluster I owns trace A, cluster II owns trace B, and so on. A cluster that owns a trace executes all instructions in that trace. On the other hand, a cluster that does not own a trace does not execute the branches, stores, and predicted-ineffectual instructions of that trace. In other words, it executes all predicted-effectual instructions

other than predicted-effectual stores and predicted-effectual branches, shown below for A".

The same logic applies to other traces.

Figure 4-4: Replication of effectual component with store distribution.

Below are the key changes that must be introduced in the microarchitecture for implementing this scheme (in addition to the changes described for the previous scheme).

• After fetching an instruction, it is dispatched to all clusters if it is predictedeffectual (except for predicted-effectual branches/stores), or steered to one of the clusters (depending on the owner of the trace) if it is predicted-ineffectual or a predicted-effectual branch/store.

#### **4.3 Dedicated Cluster for Effectual Component (DEC0)**

We propose another model for eliminating inter-cluster communication between effectual instructions: All predicted-effectual instructions are executed on a single dedicated cluster and all predicted-ineffectual instructions are steered to clusters other than the dedicated cluster to which effectual instructions are steered. In this way, intercluster communication between effectual instructions is eliminated, except in the rare case of an IR-misprediction (since an effectual instruction is misclassified as an ineffectual instruction and steered to a different cluster). Ineffectual instructions, which depend on both effectual and ineffectual instructions, experience delays in execution due to inter-cluster communication latency. As these instructions are less critical, these delays can be tolerated. Note that the advantage of this model with respect to the previous models is that computation is compressed to just the effectual component on the dedicated cluster. On the other hand, ineffectual instructions must now wait longer for values from effectual instructions, since the effectual component is not replicated on all clusters.

Figure 4-5 shows how this heuristic works for a quad-cluster configuration. The dynamic instruction stream is broken into two components, predicted-effectual and

predicted-ineffectual instructions. All predicted-effectual instructions are steered to a single cluster, i.e., cluster I. This cluster, which is designated solely for the purpose of executing effectual instructions, is called the *effectual cluster*. All ineffectual instructions are steered to clusters other than the effectual cluster, i.e., clusters II, III, and IV, on the basis of dependence-based steering.

Figure 4-5: Dedicated cluster for effectual component.

Since there is no replication, no additional changes to the clustered microarchitecture are needed other than basing steering on effectualness.

# 4.4 Dedicated Cluster for Effectual Component with Store Distribution (DECS)