H3

Overview

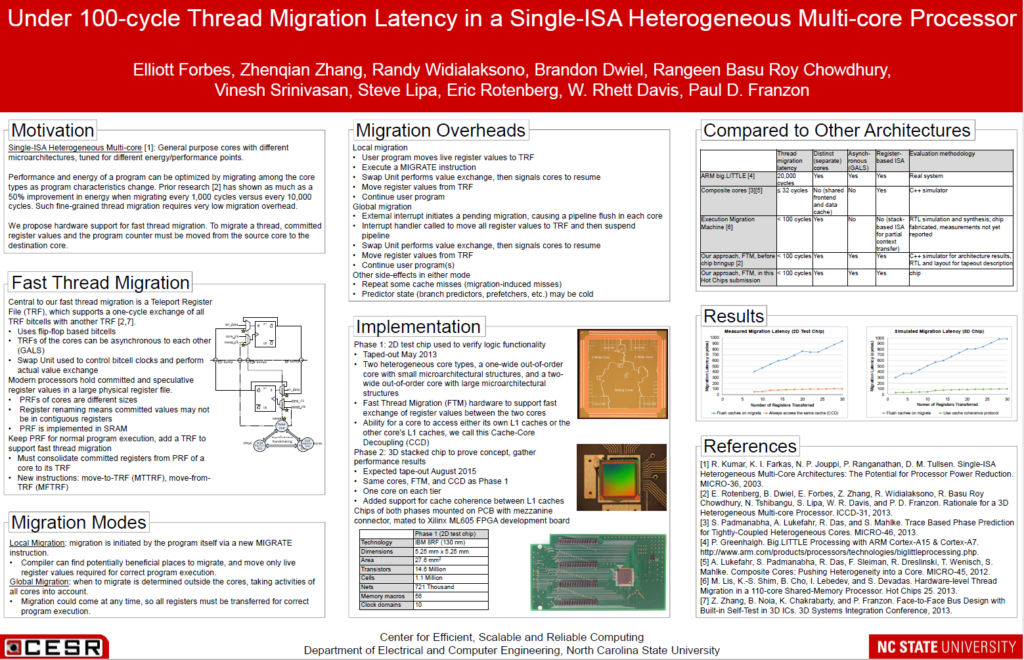

We are currently researching applications and fabricating prototypes of H3, a 3D heterogeneous multi-core processor. We have measured under 100-cycle thread migration latency between two heterogeneous OOO cores in both a precursor 2D chip and the final 3D chip

Hardware

Publications

Conference and Journal Papers

V. Srinivasan, R. Basu Roy Chowdhury, E. Forbes, R. Widialaksono, Z. Zhang, J. Schabel, S. Ku, S. Lipa, E. Rotenberg, W. R. Davis, and P. D. Franzon. H3 (Heterogeneity in 3D): A Logic-on-logic 3D-stacked Heterogeneous Multi-core Processor. Proceedings of the 35th IEEE International Conference on Computer Design (ICCD-35), pp. 145-152, November 2017. [pdf]

R. Widialaksono, R. Basu Roy Chowdhury, Z. Zhang, J. Schabel, S. Lipa, E. Rotenberg, W. R. Davis, and P. D. Franzon. Physical Design of a 3D-stacked Heterogeneous Multi-Core Processor. Proceedings of the 2016 IEEE International 3D Systems Integration Conference (3DIC’16), pp. 1-5, November 2016. [pdf]

E. Forbes and E. Rotenberg. Fast Register Consolidation and Migration for Heterogeneous Multi-core Processors. Proceedings of the 34th IEEE International Conference on Computer Design (ICCD-34), pp. 1-8, October 2016. [pdf]

Best Paper Award in the Processor Architecture Track

E. Rotenberg, B. H. Dwiel, E. Forbes, Z. Zhang, R. Widialaksono, R. Basu Roy Chowdhury, N. Tshibangu, S. Lipa, W. R. Davis, and P. D. Franzon. Rationale for a 3D Heterogeneous Multi-core Processor. Proceedings of the31st IEEE International Conference on Computer Design (ICCD-31), pp. 154-168, October 2013. [pdf]

Workshop Papers and Presentations

E. Forbes, R. Basu Roy Chowdhury, B. Dwiel, A. Kannepalli, V. Srinivasan, Z. Zhang, R. Widialaksono, T. Belanger, S. Lipa, E. Rotenberg, W. R. Davis, and P. D. Franzon. Experiences with Two FabScalar-based Chips.6th Workshop on Architectural Research Prototyping (WARP’15), in conjunction with ISCA-42, June 14, 2015.

[paper (pdf), presentation (ppt)]

Poster Presentations

E. Forbes, Z. Zhang, R. Widialaksono, B. Dwiel, R. Basu Roy Chowdhury, V. Srinivasan, S. Lipa, E. Rotenberg, W. R. Davis, and P. D. Franzon. Under 100-cycle Thread Migration Latency in a Single-ISA Heterogeneous Multi-core Processor. Poster session of Hot Chips 2015, August 23-25, 2015. [poster (pdf)]

Student Theses

J. E. Forbes. Hardware Thread Migration for 3D Die-stacked Heterogeneous Multi-core Processors. Ph.D. Thesis, Department of Electrical and Computer Engineering, North Carolina State University, March 2016. [NCSU library: on-line thesis]

V. Srinivasan. Phase II Implementation and Verification of the H3 Processor. M.S. Thesis, Department of Electrical and Computer Engineering, North Carolina State University, August 2015. [NCSU library: on-line thesis]

Talks

Experiences with Two FabScalar-based Chips. Presented at WARP on June 14, 2015, by E. Forbes (H3 project) and R. Basu Roy Chowdhury (AnyCore project). [ppt]

Funding

This project is supported by Intel.