AnyCore

Overview

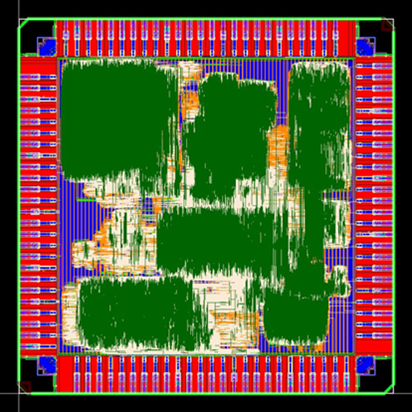

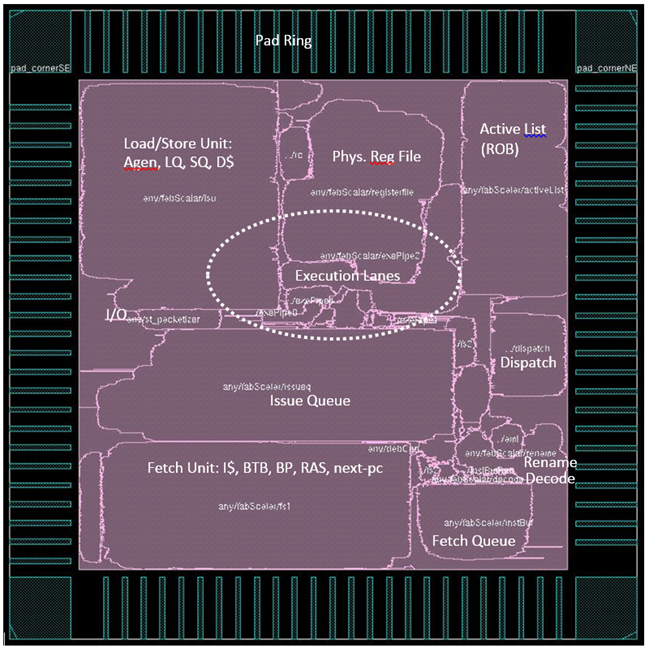

AnyCore is two things: an ideal called a “universal superscalar core”, and a tool that enables research towards this ideal. A universal superscalar core is a single core that can mimic arbitrary fixed cores in a large superscalar design space, defined by superscalar structure sizes, superscalar widths, and pipeline depth. Each of its hundreds of core configurations achieves the same instructions-per-cycle (IPC), frequency, and energy consumption as the corresponding fixed core design, had that fixed core been individually fabricated. In other words, a universal superscalar core is “core-accurate” with respect to hundreds or thousands of fixed cores. Pursuit of a universal superscalar core requires a hardware model of one. To this end, we developed a register-transfer-level (RTL) design of a comprehensively adaptive superscalar core, called AnyCore. The RTL description of the core is heavily parameterized, allowing AnyCore processors of different sizes to be synthesized. A given AnyCore processor is adaptive, i.e., its widths and structures can be dynamically adjusted within its maximum dimensions. The RTL description is paired with a Unified Power Format (UPF) description of power domains, which today’s EDA tools can handle for automatically synthesizing, simulating and measuring power-gated designs.

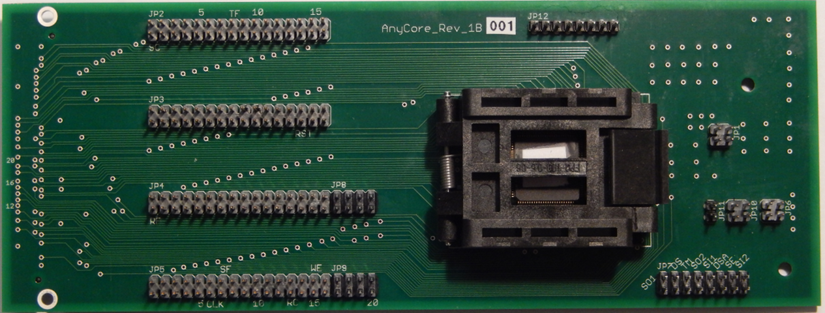

We are doing both research and chip fabrication with AnyCore.

Hardware

Publications

Conference and Journal Papers

R. Basu Roy Chowdhury, A. K. Kannepalli, S. Ku, and E. Rotenberg. AnyCore: A Synthesizable RTL Model for Exploring and Fabricating Adaptive Superscalar Cores. Proceedings of the 2016 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS’16), pp. 214-224, April 2016. [pdf]

Workshop Papers and Presentations

R. Basu Roy Chowdhury, A. K. Kannepalli, and E. Rotenberg. FabScalar-RISC-V. 2nd RISC-V Workshop, June 29-30, 2015. [presentation (pdf)]

E. Forbes, R. Basu Roy Chowdhury, B. Dwiel, A. Kannepalli, V. Srinivasan, Z. Zhang, R. Widialaksono, T. Belanger, S. Lipa, E. Rotenberg, W. R. Davis, and P. D. Franzon. Experiences with Two FabScalar-based Chips.6th Workshop on Architectural Research Prototyping (WARP’15), in conjunction with ISCA-42, June 14, 2015.

[paper (pdf), presentation (ppt)]

Poster Presentations

R. Basu Roy Chowdhury, A. Kannepalli, and E. Rotenberg. AnyCore-1: A Comprehensively Adaptive 4-way Superscalar Processor. Poster session of Hot Chips 2016, August 21-23, 2016. [poster (pdf)]

Technical Reports

Student Theses

R. Basu Roy Chowdhury. AnyCore: Design, Fabrication, and Evaluation of Comprehensively Adaptive Superscalar Processors. Ph.D. Thesis, Department of Electrical and Computer Engineering, North Carolina State University, September 2016. [NCSU library: on-line thesis]

A. K. Kannepalli. Chip Bringup of the AnyCore Adaptive Superscalar Core. M.S. Thesis, Department of Electrical and Computer Engineering, North Carolina State University, July 2015. [NCSU library: on-line thesis]

Talks

FabScalar-RISC-V. Presented at 2nd RISC-V Workshop on June 30, 2015, by R. Basu Roy Chowdhury. [pdf]

Experiences with Two FabScalar-based Chips. Presented at WARP on June 14, 2015, by E. Forbes (H3 project) and R. Basu Roy Chowdhury (AnyCore project). [ppt]

Funding

This project is supported by NSF grant CCF-1018517 (AnyCore: A Universal Superscalar Core), and a Qualcomm gift.

Any opinions, findings, and conclusions or recommendations expressed in this website and publications herein are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.