#### The State of ZettaRAM

# Eric Rotenberg and Ravi K. Venkatesan\*

Center for Embedded Systems Research (CESR)

Department of Electrical and Computer Engineering

North Carolina State University

www.tinker.ncsu.edu/ericro

\* Now at Intel Bangalore

#### **Goal of Talk**

- ➤ High level (casual) talk about ZettaRAM

- ➤ Consolidate papers and patents

- Core technology

- Three different embodiments

- Key novel properties

- Implications

# **Core Technology**

- ➤ New memory from ZettaCore

- Genesis in DARPA Moletronics

- Molecule stores 1 charge (0, +1)

- Some molecule types store multiple charges (0, +1, +2)

####

- ➤ Long term

- 1 molecule = 1 bit

- > Near term

- Use molecules in aggregate

- Molecular capacitor

#### **ZettaRAM Molecular Capacitor**

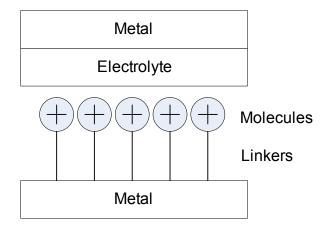

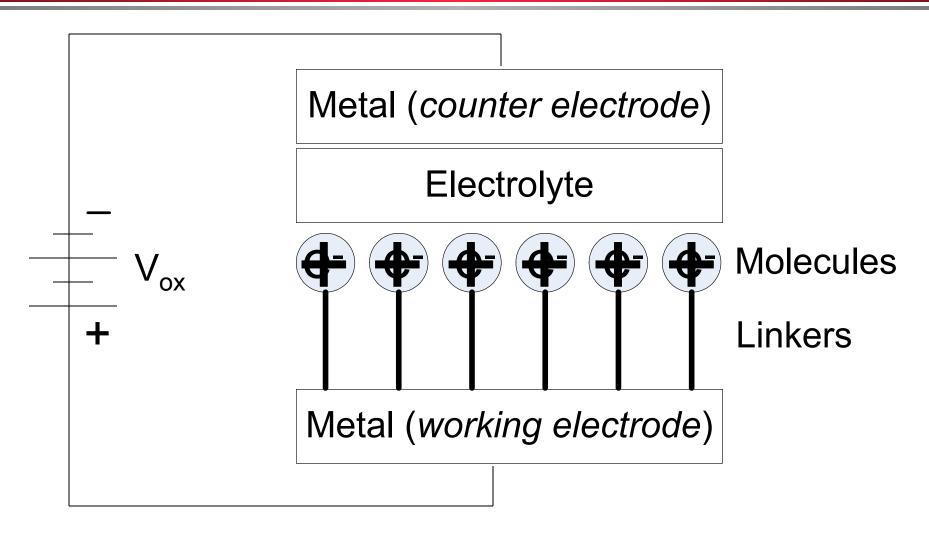

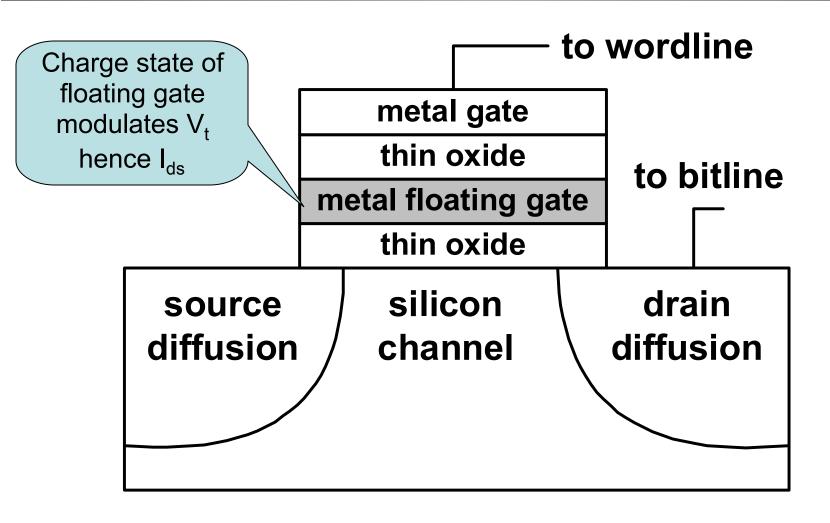

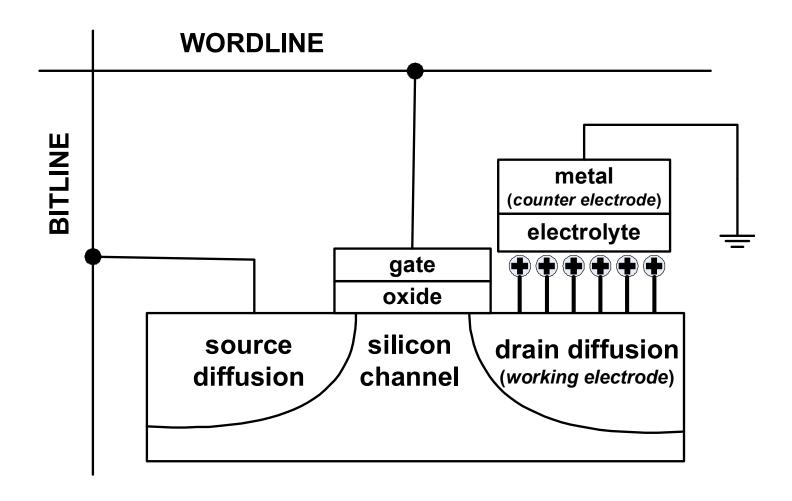

## **Molecular Capacitor**

## Linker & Electrolyte

- ➤ Neither conduct electrons

- > Electrons tunnel across linker

- ➤ Electrolyte ions form aligned dipoles

- Electrically interface counter electrode to molecules, yet charged molecules isolated

- Also provide critical charge shielding, prevent huge electric field across short linkers

- Intrinsic retention times of 10s of seconds to minutes

### **Three Embodiments**

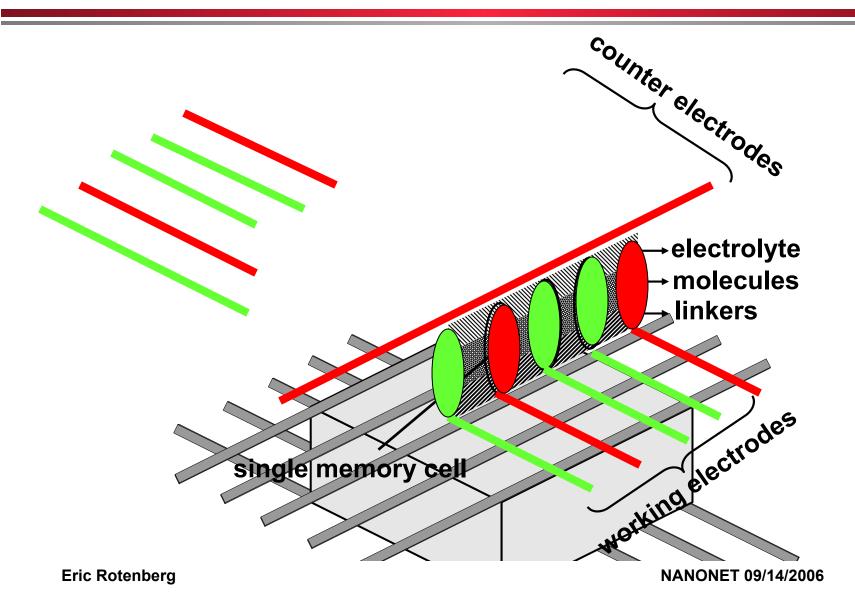

- **>**Transistor-free **Crossbar**

- ➤ Two hybrid molecule/silicon devices

- Flash-like MoleFET

- 1T-1C DRAM cell with molecular capacitor

## Crossbar

### **Crossbar Features**

- ➤No explicit patterning of cells

- Cell forms implicitly between electrodes

- Density only limited by wire pitch

- Easy path to minimum DRAM density

- >Silicon free

- Easy 3D stacking (no silicon growth)

- Deposit on arbitrary surfaces? Flexible memory?

### **Crossbar Fate**

- ➤ Crossbar earliest embodiment

- >2x2 in the lab

- ➤ Repeatability issues?

- Disturbs due to floating electrode voltages

- Better control with transistor switches at intersections

- ➤ Meanwhile

- Moletronics 2nd phase brought transistor fab engineers

- Shift towards hybrid molecules/silicon

- Leverage predominance of silicon fabrication

## **Conventional Flash Memory**

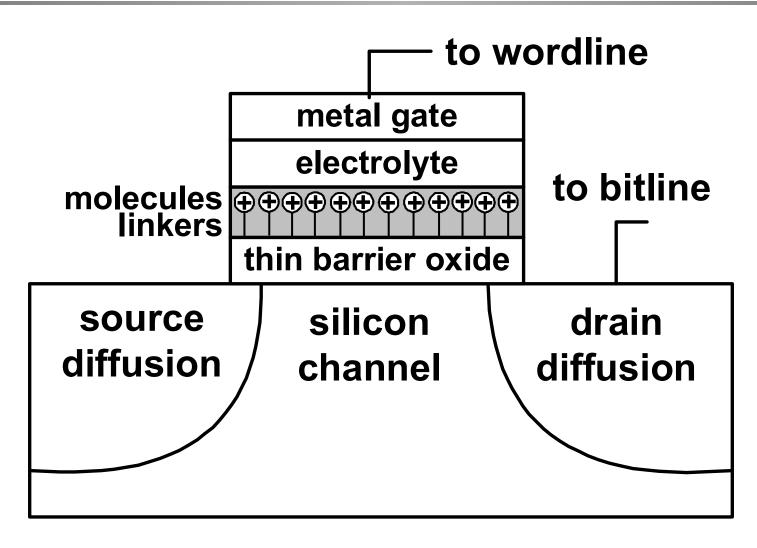

## **MoleFET Flash Memory**

### **MoleFET Features**

- > Fixed charge provides discreteness

- Remarkable accuracy compared to "continuous" floating gate

- Robust, work within tighter noise margins

- Path to smaller devices

- ➤ Discreteness especially benefits multi-bit storage

- Multi-bit successful in Flash domain

- Molecules with multiple discrete charge states makes multi-bit much easier

$$V_{prog} > V_{ox3}$$

$V_{prog} > V_{ox2}$

$V_{prog} > V_{ox1}$

### MoleFET Issues

> Striving for larger V<sub>t</sub> shift

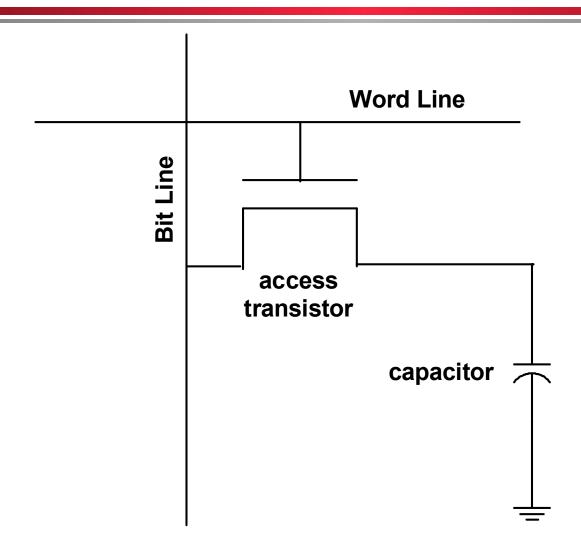

### **Conventional 1T-1C DRAM Cell**

Eric Rotenberg NANONET 09/14/2006

#### **1T-1C DRAM Derivative**

## **DRAM Voltage Scaling Limits**

#### ZettaRAM's Power Scaling Advantage

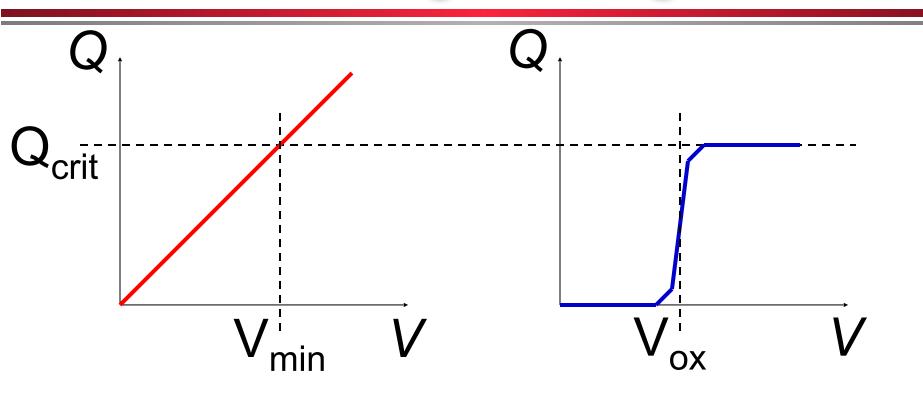

- ➤ Q<sub>crit</sub> nearly constant due to noise sources

- Sense amp margins

- Bitline imbalances

- Leakage

- Radiation

- ➤ Conventional DRAM

- Charge-voltage coupling, Q = CV

- Charge constrains voltage

- >ZettaRAM derivative

- Charge-voltage decoupling

- Fixed charge independent of voltage

- Charge does not constrain voltage

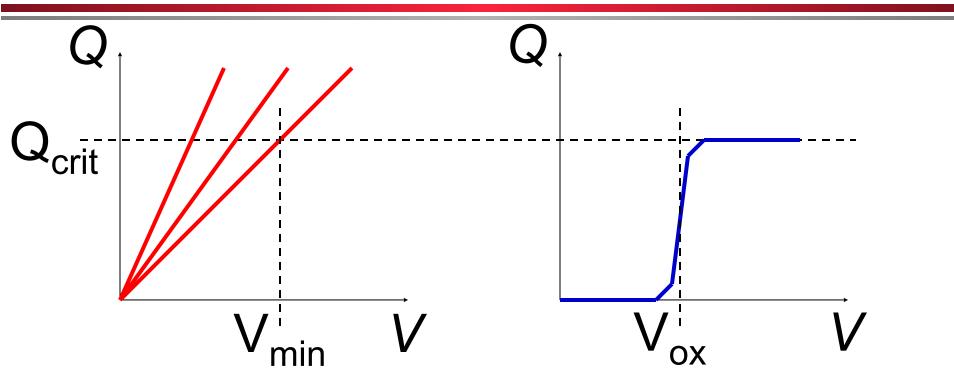

## **DRAM Voltage Scaling Limits**

- Hard to increase C

- Even harder when reducing 2D area

- Engineer new molecules with lower thresholds

## **Key Properties**

- ➤ Flexibility and Precision

- ➤ Self-Assembly

- ➤ Charge-Voltage Decoupling

- ➤ Speed/Energy Tradeoff

- ➤ Multiple Discrete States

- >> Admixtures

## Flexibility and Precision

- > Hundreds of molecules synthesized

- > Significant flexibility in customizing molecular attributes

- Design of organic molecules

- Design of attachment groups

- Influence surface concentration (density), threshold voltage (power), electron transfer rate (speed, retention time)

- > Semiconductors also flexible

- But attributes (e.g., threshold voltage) depend on bulk properties

- Sophisticated "recipes" required

- High cost to achieve precision

- Contrast bulk properties with intrinsic chemical properties of molecules

## **Self-Assembly**

- > Auto arrangement of molecules in single, uniform, dense monolayer

- Autonomous and parallel

- Efficient fabrication

- Reconsider possibilities thought impractical with conventional tech.

- Mixed logic/DRAM chips (DRAM embodiment)

- Conventional logic and DRAM processes too different due to stacked capacitors

- Self-assembled monolayers yield high charge density without elaborate stacked capacitor structures

- Apply thin oxide concept of MoleFET to reduce leakage (speed tradeoff)

- > 3D stacking (crossbar embodiment)

- Molecules self-assemble on any compatible surface

- Easy path to 3D memory stacking

## **Charge-Voltage Decoupling**

- > Fixed charge independent of voltage

- ➤ Charge does not constrain voltage

- ➤ Power-scalable DRAM derivative extends roadmap of this important memory technology

Eric Rotenberg NANONET 09/14/2006

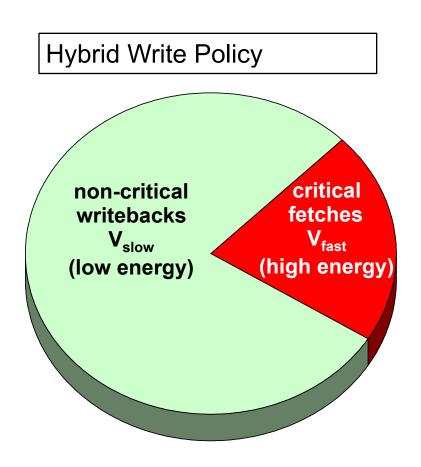

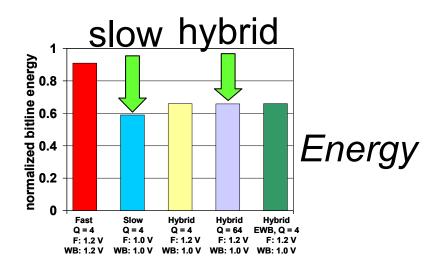

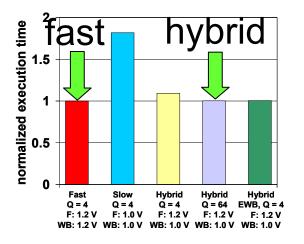

## **Speed/Energy Tradeoff**

- ➤ Voltage padded with respect to V<sub>ox</sub>

- Molecule speed slower as voltage approaches V<sub>ox</sub>

- Pad write voltage for competitive latency

- ➤ Opportunity for architectural management

- Apply "fast voltage" for critical requests and "slow voltage" for non-critical requests

NANONET 09/14/2006

## Intelligent Management

Time

25

## **Multiple Discrete States**

- ➤ Easier multi-bit storage due to discrete states

- ➤ Discreteness reduces variability

Eric Rotenberg NANONET 09/14/2006

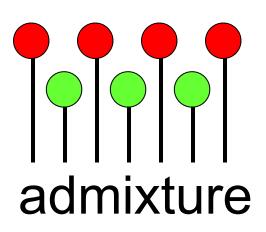

#### **Admixtures**

- > Different molecules can be mixed in same chip

- ➤ Although hybrid technologies not new:

- Nanotechnology offers new twist

- Different molecules can occupy same physical space

#### **Dual Molecules**

primary storage molecule

E. Rotenberg and J. Lindsey. Variable-Persistence Molecular Memory Devices and Methods of Operation Thereof. US Patent #6,944,047.

primary storage molecule

secondary storage molecule

#### **Possibilities**

- ➤ Unusual memory hierarchy

- Memories with different attributes (speed, power, volatility) cohabit same space

- New challenges and opportunities for optimizing data "placement" for power and performance

- >Admixtures enable different business models

- Ship product with multiple molecules but only one configured

- Multiple virtual products in one physical product

#### The State of ZettaRAM

#### > Contribution

- Consolidated and distilled papers and patents

- Unified discussion of core technology, embodiments, key properties, and implications

- ZettaRAM has signs of disruptive technology

- Cheap fabrication of high perf. memory (by all metrics)

- Practical mixed logic/DRAM

- Practical 3D memory

- Exceeds DRAM power scaling limits

- Intelligent power management

- Efficient multi-bit storage

- Memory hierarchies cohabiting same space

- Multiple virtual products in one physical product

Eric Rotenberg NANONET 09/14/2006